# CompactRISC

CR16A Programmer's Reference Manual

> Part Number: 424521426-006 February 1997

## **REVISION RECORD**

### SUMMARY OF CHANGES

1.0 1.1 August 1996 February 1997

RELEASE DATE

First release. Minor modifications and corrections.

## PREFACE

This Programmer's Reference Manual presents the programming model for the CR16A microprocessor core. The key to system programming, and a full understanding of the characteristics and limitations of the CompactRISC Toolset, is understanding the programming model.

The information contained in this manual is for reference only and is subject to change without notice.

No part of this document may be reproduced in any form or by any means without the prior written consent of National Semiconductor Corporation.

## CONTENTS

| Chapter | 1 IN1 | TRODUCTION                                  |      |

|---------|-------|---------------------------------------------|------|

| 1.1     | MANU  | AL ORGANIZATION                             | 1-5  |

| 1.2     | REFE  | RENCES                                      |      |

| 1.3     | THE C | ORE                                         | 1-6  |

| Chapter | 2 PR  |                                             |      |

| 2.1     | DATA  | TYPES                                       | 2-1  |

| 2.2     | INSTR | UCTION SET                                  | 2-1  |

| 2.3     | REGIS | STER SET                                    | 2-3  |

|         | 2.3.1 | General Purpose Registers                   | 2-4  |

|         | 2.3.2 | Dedicated Address Registers                 |      |

|         | 2.3.3 | The Processor Status Register               | 2-4  |

|         | 2.3.4 | The Configuration Register                  | 2-6  |

| 2.4     | MEMC  | ORY ORGANIZATION                            | 2-7  |

|         | 2.4.1 | Data References                             |      |

|         | 2.4.2 | Stacks                                      | 2-8  |

| 2.5     | ADDR  | ESSING MODES                                | 2-9  |

| Chapter | 3 EX  | CEPTIONS                                    |      |

| 3.1     | INTRO | DUCTION                                     |      |

|         | 3.1.1 | Interrupt Handling                          |      |

|         | 3.1.2 | Traps                                       |      |

| 3.2     | EXCE  | PTION PROCESSING                            |      |

|         | 3.2.1 | Instruction Endings                         |      |

|         | 3.2.2 | Acknowledging an Exception                  |      |

|         | 3.2.3 | Exception Service Procedures                |      |

|         | 3.2.4 | Returning From Exception Service Procedures |      |

|         | 3.2.5 | Priority Among Exceptions                   | 3-7  |

|         | 3.2.6 | Nested Interrupts                           | 3-9  |

| 3.3     | RESE  | т                                           | 3-10 |

| Chapter | 4 AD  | DITIONAL TOPICS                             |      |

| 4.1     | DEBU  | GGING SUPPORT                               | 4-1  |

|         |       |                                             |      |

CompactRISC CR16A Programmer's Reference Manual

CONTENTS -v

|         | 4.1.1 | Instruction Tracing              | 4-1 |

|---------|-------|----------------------------------|-----|

|         | 4.1.2 | In-System Emulator (ISE) Support | 4-2 |

| 4.2     | INSTR | UCTION EXECUTION ORDER           | 4-3 |

|         | 4.2.1 | The Instruction Pipeline         | 4-4 |

|         | 4.2.2 | Serializing Operations           | 4-5 |

| Chapter | 5 INS | STRUCTION SET                    |     |

| 5.1     | INSTR | UCTION DEFINITIONS               | 5-1 |

##

- Appendix A INSTRUCTION SET ENCODING

- Appendix B CR16 INSTRUCTION SET

INDEX

CompactRISC CR16A Programmer's Reference Manual

CONTENTS -vi

## **FIGURES**

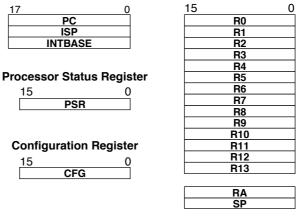

| Figure 2-1.  | CR16A Registers2-3                                                          |

|--------------|-----------------------------------------------------------------------------|

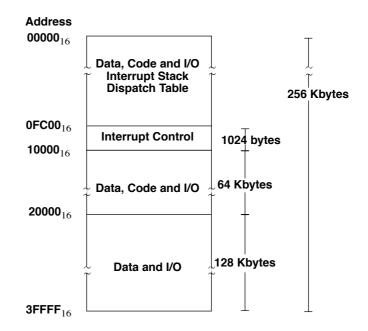

| Figure 2-2.  | Processor Status Register                                                   |

| Figure 2-3.  | Configuration Register2-6                                                   |

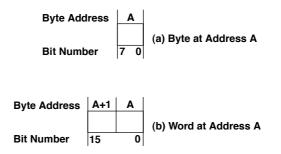

| Figure 2-4.  | Memory Organization                                                         |

| Figure 2-5.  | Data Representation                                                         |

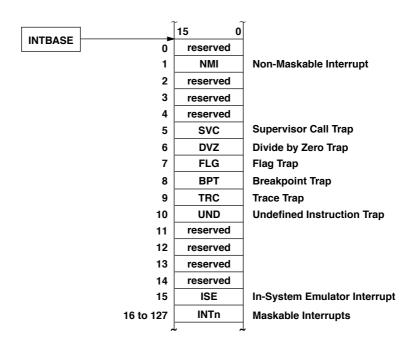

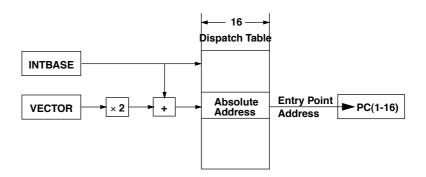

| Figure 3-1.  | Dispatch Table                                                              |

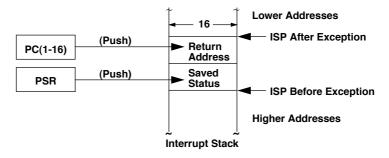

| Figure 3-2.  | Saving the PC and PSR Contents During an Exception Acknowledge Sequence 3-5 |

| Figure 3-3.  | Transfer of Control During an Exception Acknowledge Sequence                |

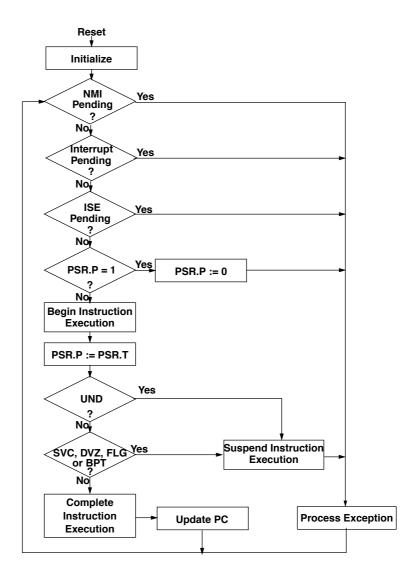

| Figure 3-4.  | Exception Processing Flowchart                                              |

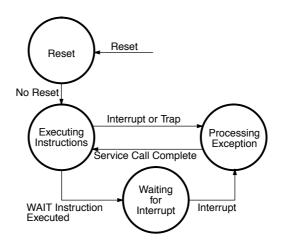

| Figure 4-1.  | CR16A Operating States4-3                                                   |

| Figure 4-2.  | Memory References for Consecutive Instructions                              |

| Figure 5-1.  | Instruction Header Format                                                   |

| Figure 5-2.  | Instruction Example Format                                                  |

| Figure A-1.  | Basic Instruction Structure                                                 |

| Figure A-2.  | Register to Register Format                                                 |

| Figure A-3.  | Short Immediate Value to Register Format                                    |

| Figure A-4.  | Medium Immediate Value to Register Format                                   |

| Figure A-5.  | Format for Instructions with Special or No Operands                         |

| Figure A-6.  | Load/Store Format, Relative with Short Displacement Value                   |

| Figure A-7.  | Load/Store Format, Relative with Medium Displacement Value                  |

| Figure A-8.  | Load/Store Format, Far-Relative                                             |

| Figure A-9.  | Load/Store Format, Absolute                                                 |

| Figure A-10. | BR or Bcond Format, Short Displacement Value                                |

| Figure A-11. | BR or Bcond Format, Medium Displacement Value                               |

| Figure A-12. | BAL Format                                                                  |

| Figure A-13. | JUMP and Jcond Instruction Format                                           |

| Figure A-14. | JAL Instruction Format                                                      |

|              |                                                                             |

## TABLES

| Table 3-1. | Summary of Exception Processing                     | . 3-6       |

|------------|-----------------------------------------------------|-------------|

| Table A-1. | Coding for Load and Store Op code and Register Type | .A-4        |

| Table A-2. | Undefined Op Codes                                  | .A-7        |

| Table A-3. | Notation Conventions for Instruction Set Summary    | .A-8        |

| Table A-4. | Instruction Encoding                                | <b>\-10</b> |

## Chapter 1 INTRODUCTION

National Semiconductor's CompactRISC architecture is a RISC architecture specifically designed for embedded systems. CompactRISC technology features compact code generation, low power consumption, silicon-efficient implementations, the ability to tightly integrate on-chip acceleration, I/O and memory functions, and scalability from 8- to 64-bits.

CISC to RISC migration The past decade has seen a gradual migration from CISC to RISC architectures. The silicon required to support CISC CPUs is too large, consumes too much power and is too expensive.

> RISC architectures execute a small set of basic instructions to achieve higher performance with less silicon. This yields smaller, more economical silicon solutions that use less power, and provide higher performance. Higher frequency clock speeds further improve performance. Higher clock speeds require advanced concurrent processing techniques that allow simultaneous and overlapping execution of instructions. The most obvious of these is a multistage pipeline structure.

> Modern RISC architectures are optimized for High Level Language (HLL) programs, usually written in C, and powerful, multiuser, multitasking operating systems such as UNIX and Windows. In these applications, processing speed is the most important consideration. As a result, modern RISC architectures are designed for "hyper" clock speeds with extensive, overlapping execution logic which yield highly optimized processors for workstation and fileserver applications.

However, existing RISC architectures are not well suited for embedded systems applications.

**Embedded** Embedded systems, being application specific, require a low system cost, while delivering sufficient performance for the application. They usually integrate on-chip memory and I/O with the processor. Clock frequency is limited by EMI and noise.

These system constraints dictate the requirements for embedded processors. In the past, general-purpose CISC processors were modified to serve this market. The resulting microcontroller architectures provided low-cost, highly-integrated systems, but at a cost. The architectures were convoluted, difficult to program using high-level languages, and not scalable from one data-path width to the next.

CompactRISC CR16A Programmer's Reference Manual

Embedded CISC microcontrollers were, however, successful because they met other important criteria of embedded systems:

- Low total system cost

- On-chip memory and I/O functions

- Small code size

Present RISC processors are optimized for use as computer CPUs, and are thus not a perfect fit for embedded systems. An emphasis on speed, and high-speed concurrent operation logic, yields large silicon implementations. Large off-chip memories and I/O require large on-chip bus interface units that further increase silicon size. Finally, the use of consistent fixed-width instructions simplifies the processor design, but increases code size, and the size of ROM, as compared with CISC architectures.

National's CompactRISC technology approach Based on its experience with many high-volume designs using its previous 8-bit and 16-bit microcontroller and 32-bit CISC embedded processor families, National concluded that there was a need for a new class of high-performance embedded control systems. Such processors are suited for moving and shaping information applications such as wireless communication systems, multifunction peripherals, automotive subsystems, printers and fax machines, games, mass storage subsystems, communication switches and encryption devices. These applications require significant processing power and powerful development tools (for faster time to market), but must meet stringent cost and power consumption constraints.

To meet this need, National developed a new RISC processor technology that combines the advantages of RISC with the compact code generation of CISC, and is scalable from 8 bits to 64 bits.

In developing the CompactRISC technology, National had to rethink the process of traditional RISC architecture design. In analyzing RISC design against the goals of embedded systems design, CompactRISC architects found several ways to greatly reduce the amount of silicon required without significantly reducing the performance advantages of RISC.

CompactRISC Architecture Characteristics:

- Reduced concurrency logic

- Smaller bus interface units

- Smaller transistor count

We made a number of observations which affected the basic architectural decisions:

• Workstation-oriented RISC architectures trade silicon efficiency for instruction execution efficiency.

Traditional RISC architectures squeeze every bit of execution time

CompactRISC CR16A Programmer's Reference Manual

from a fast system clock by using overlapping pipelines and highly parallel concurrent logic. However, this greatly increases both the number of on-chip transistors required, and the die size.

The performance needs of embedded controllers are quite different. There is less pressure to squeeze clock performance through every available design trick. CompactRISC eliminates a large amount of costly pipeline control logic just by reducing the number of pipeline stages from five, or more, to three. Shorter pipeline organization allows eliminating branch prediction mechanisms and bypass registers, while maintaining an acceptable overall performance level for embedded systems.

- Traditional RISC systems used large off-chip memory and I/O, requiring large and complex on-chip bus interface units. Embedded systems use on-chip memory wherever possible. Thus, the CompactRISC is designed with a minimum bus interface unit to onchip memories. A controller for external memory accesses is added only when off-chip memory is needed. A separate peripheral bus controller is optimized for on-chip I/O. This approach yields maximum resource flexibility with minimum silicon overhead.

- Designs optimized for clock speeds of 100 MHz, or higher, required much greater margins in the basic transistor design. National realized that the overwhelming majority of embedded systems face EMI and noise problems that prohibit clock speeds in excess of 25 MHz, and designed the CompactRISC with transistors and signal paths optimized for clock speeds of 30 MHz, and lower.

These observations led to a less complex, and much tighter, silicon implementation. Because the CompactRISC core has fewer transistors than other RISC processors, there are fewer transistors to drive, reducing the size of internal bus drivers. The cumulative effect of fewer and smaller transistors, with a slower clock, yields dramatically smaller silicon, with lower system costs, and significantly lower power consumption.

#### Reduced memory requirements

RISC architectures have traditionally used fixed-width instructions to simplify instruction decoder design. In 32-bit RISC systems, instructions are either four or eight bytes. CISC systems use a variable instruction length, resulting in smaller code size for a given application. The CompactRISC uses variable instruction widths, with fixed coding fields within the instruction itself. For example, the opcode field is always in the first 16 bits, with additional bytes as required for immediate values. Instructions for the 32-bit CompactRISC core may be 2-bytes, 4bytes or 6-bytes long, but basic instructions are only two bytes long. This permits optimized instruction processing by the instruction decoder, and results in a smaller code size. The size of code generated for the CompactRISC core is comparable to CISC code size, or typically 25 percent smaller than code generated for a typical RISC CPU.

Standard 32-bit RISC processors deliver high performance only when aligned 32-bit data is used. Intermediate results are stored in memory as 32-bit values and registers are saved as 32-bit operands on the stack. CompactRISC CR32 instructions operate on 8-, 16- and 32-bit data. Nonaligned accesses are allowed. Dedicated data type conversion instructions speed data access to mixed size data. With smaller code size, and variable length instructions and data, the CompactRISC family makes more efficient use of smaller, lower cost, lower bandwidth memories. Smaller memories allow many more system elements to be integrated with on-chip memory.

Scalable cores These architectural features make the CompactRISC technology ideal from 8 to 64 bits for the next generation of embedded systems. In addition, National decided to implement the CompactRISC technology in a set of core processors, in the range 8- to 64-bits. This provides a new, more attractive solution for designers of low-end embedded systems.

> Low-cost, single-chip systems, with on-board memory and I/O, could be implemented with low-cost 8-bit microcontrollers, or later 16-bit versions. However, the accumulator-based architectures of such microcontrollers made programming in high-level languages impractical. Code generated by a compiler for such machines is typically larger, and slower than code written in assembly language.

> The CompactRISC's architecture, however, produces highly efficient compiler generated code. CompactRISC is the first architecture designed to produce highly efficient HLL-generated code in both the 8- and 16-bit worlds.

> With National's compatible family of processor cores, the designer of embedded controller-based systems can now choose the optimum processor size for a given target application. This is particularly useful in leveraging the development investment across several classes of related end-products. With a single processor family, a number of different products can be developed with a single development platform and using the same HLL-based development and debug tools.

Fast HLL development and debug

With the CompactRISC technology, unlike previous microcontroller families, you can develop code, and debug, in C, greatly speeding up the development process. In today's marketplace, with some product life cycles lasting 9 to 18 months or less, working with HLL "power tools" is a significant advantage. A single development platform, for a wide range of systems from low-end to high-end, is also an important advantage. The designer of CompactRISC-based systems can maintain a single set of software development tools covering all CompactRISC implementations.

#### **CompactRISC architecture** In many ways, CompactRISC technology is a traditional RISC load/store processor architecture. For example, the CR16 executes an optimized instruction set with 21 internal registers grouped in 16 general purpose registers, three dedicated address registers, a processor status register and a configuration register. A three-stage pipeline is used to obtain a peak performance of 30 Million Instruction Per Second (MIPS) at a clock frequency of 30 MHz.

The CompactRISC core includes a pipelined integer unit that supports a peak execution speed of one instruction per each internal cycle, with a 60 Mbyte/sec. (CR16) or 120 Mbyte/sec. (CR32) pipelined bus. The CompactRISC technology supports little-endian memory addressing. This means that the byte order in a CompactRISC processor is from least significant byte to the most significant byte.

**Debug support** The CompactRISC provides instruction tracing, soft breakpoints via breakpoint instructions and external ISE support.

You use instruction tracing, during debugging, to single-step through a program. Two bits in the PSR or Program Status Register enable and generate trace traps. In addition, you can use a breakpoint instruction (EXCP BPT) to stop execution of a program at specified instructions, allowing the debugger to examine the status of the program and internal registers. The CompactRISC also supports an input pin that causes an ISE interrupt. The core processor then provides status signals that are activated upon completing an instruction. Finally, the CR32 also has on-chip hardware breakpoint support for data and address values.

#### 1.1 MANUAL ORGANIZATION

This reference manual describes the CR16A core, as follows:

- **Chapter 1** "INTRODUCTION" introduces the CompactRISC architecture.

- **Chapter 2** "PROGRAMMING MODEL" presents the instruction set, the register set, operands and addressing modes of the core.

- **Chapter 3** "EXCEPTIONS" introduces traps and interrupts in the core, and describes the way these exceptions are treated.

- **Chapter 4** "ADDITIONAL TOPICS" covers more advanced concepts related to the CR16A programming model: the CR16A debugging features and the use of the CR16A pipeline.

- **Chapter 5** "INSTRUCTION SET" describes all the instructions provided by the CR16A core.

- Appendix A "INSTRUCTION SET ENCODING"

CompactRISC CR16A Programmer's Reference Manual

### 1.2 REFERENCES

Core Bus Specification., National Semiconductor, December 1994.

## 1.3 THE CORE

The CR16A core is designed to operate with other Very Large Scale Integrated (VLSI) modules such as a bus interface unit, ROM, RAM, and peripherals. Together with such modules, a CR16A based integrated circuit, implements a full microcontroller or microprocessor.

The CR16A is designed to obtain the maximum performance from Very Large Scale Integration (VLSI), pipelining, and optimizing compilers. The high performance of the CR16A microprocessor results from the implementation of a pipelined architecture with state-of-the-art VLSI CMOS technology.

The CR16A supports a peak execution speed of one instruction each clock cycle and a two byte/cycle pipelined system bus.

# Chapter 2 PROGRAMMING MODEL

### 2.1 DATA TYPES

**Integer Data Type**The integer data type is used to represent integers. Integers may be signed or unsigned. Two integer sizes are supported: 8-bit (1 byte), and 16-bit (1 word). Signed integers are represented as binary two's complement numbers and have values in the range  $-2^7$  to  $2^7-1$  and  $-2^{15}$  to  $2^{15}-1$ , respectively. Unsigned numbers have values in the range 0 to  $2^8-1$  and 0 to  $2^{16}-1$ , respectively.

Boolean DataThe boolean data type is represented as an integer (byte or word). The<br/>value of its least significant bit represents one of two logical values, true<br/>or false. Integer 1 indicates true; integer 0 indicates false.

#### 2.2 INSTRUCTION SET

This section includes a summary list of all the instructions in the CR16A instruction set. Chapter 5, "INSTRUCTION SET" describes each instruction in detail.

The following instructions are included in the CR16A:

|    | Mnemonic | Operands        | Description              |

|----|----------|-----------------|--------------------------|

| MO | VES      |                 |                          |

|    | MOVi     | Rsrc/imm, Rdest | Move                     |

|    | MOVXB    | Rsrc, Rdest     | Move with sign extension |

|    | MOVZB    | Rsrc, Rdest     | Move with zero extension |

#### INTEGER ARITHMETIC

| ADD[U]i | Rsrc/imm, Rdest | Add                                                    |

|---------|-----------------|--------------------------------------------------------|

| ADDCi   | Rsrc/imm, Rdest | Add with carry                                         |

| MULi    | Rsrc/imm, Rdest | Multiply                                               |

| SUBi    | Rsrc/imm, Rdest | Subtract (Rdest := Rdest - Rsrc)                       |

| SUBCi   | Rsrc/imm, Rdest | Subtract with carry<br>(Rdest := Rdest - Rsrc - PSR.C) |

#### INTEGER COMPARISON

| CMPi Rsrc/imm, Rdest Compare (Rdest – Rsrc) |

|---------------------------------------------|

|---------------------------------------------|

CompactRISC CR16A Programmer's Reference Manual

| Mnemonic          | Operands        | Description                    |

|-------------------|-----------------|--------------------------------|

| LOGICAL AND BOOLE | EAN             |                                |

| ANDi              | Rsrc/imm, Rdest | Logical AND                    |

| ORi               | Rsrc/imm, Rdest | Logical OR                     |

| Scond             | Rdest           | Save condition code as boolean |

| XORi              | Rsrc/imm, Rdest | Logical exclusive OR           |

|                   |                 |                                |

#### SHIFTS

| ASHUi | Rsrc/imm, Rdest | Arithmetic left/right shift |

|-------|-----------------|-----------------------------|

| LSHi  | Rsrc/imm, Rdest | Logical left/right shift    |

#### BITS

| TBIT | Roffset/imm, Rsrc | Test bit |

|------|-------------------|----------|

## PROCESSOR REGISTER MANIPULATION

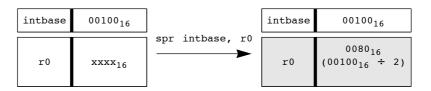

| LPR | Rsrc, Rproc  | Load processor register  |

|-----|--------------|--------------------------|

| SPR | Rproc, Rdest | Store processor register |

### JUMPS AND LINKAGE

| Bcond | disp           | Conditional branch    |

|-------|----------------|-----------------------|

| BAL   | Rlink, disp    | Branch and link       |

| BR    | disp           | Branch                |

| EXCP  | vector         | Trap (vector)         |

| Jcond | Rtarget        | Conditional Jump      |

| JAL   | Rlink, Rtarget | Jump and link         |

| JUMP  | Rtarget        | Jump                  |

| RETX  |                | Return from exception |

### LOAD AND STORE

| LOADi | disp(Rbase), Rdest          | Load (register relative)  |

|-------|-----------------------------|---------------------------|

|       | disp(Rpair+1, Rpair), Rdest | Load (far-relative)       |

|       | abs, Rdest                  | Load (absolute)           |

| STORi | Rsrc, disp(Rbase)           | Store (register relative) |

|       | Rsrc, disp(Rpair +1, Rpair) | Store (far-relative)      |

|       | Rsrc, abs                   | Store (absolute)          |

### MISCELLANEOUS

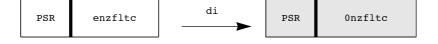

| DI   | Disable maskable interrupts |

|------|-----------------------------|

| EI   | Enable maskable interrupts  |

| NOP  | No operation                |

| WAIT | Wait for interrupt          |

CompactRISC CR16A Programmer's Reference Manual

### 2.3 REGISTER SET

This section describes each register, its bits and its fields in detail. In addition, the format of each register is illustrated.

All registers are 16 bits wide, except for the three address registers, which are 18 bits wide. Bits specified as "reserved" must be written as 0. Read operations return a value of "undefined" from reserved bits.

The CR16A has 21 internal registers grouped by function as follows:

- 16 general purpose registers

- · the following processor registers,

- 3 dedicated address registers

- 1 processor status register

- 1 configuration register

Figure 2-1 shows the internal registers of the CR16A.

#### Dedicated Address Registers General Purpose Registers

Figure 2-1. CR16A Registers

CompactRISC CR16A Programmer's Reference Manual

#### 2.3.1 General Purpose Registers

Registers R0-R13 are used for general purposes, such as holding variables, addresses or index values. The SP general purpose register is usually used as a pointer to the program run-time stack. The RA general purpose register is usually used as a return address from sub-routines. If a general purpose register is specified by an operation that is 8 bits long, then only the low part of the register is used; the high part is not referenced or modified.

#### 2.3.2 Dedicated Address Registers

This section describes the three 18-bit wide dedicated address registers that the CR16A uses to implement specific address functions.

- **PC** Program Counter The value in the PC register, points to the first byte of the instruction currently being executed. The most significant and the least significant bits of the PC are always 0. Thus CR16A instructions reside in even addresses in the address range 0 to 1FFFE<sub>16</sub>. At reset, the PC is initialized to 0 and the value of bits 1 through 16 of the PC prior to reset is saved in the R0 general purpose register.

- **ISP** Interrupt Stack Pointer The ISP register points to the lowest address of the last item stored on the interrupt stack. This stack is used when interrupt and trap service procedures are invoked. The two most significant, and the least significant bits of this register are always 0. Thus the interrupt stack always starts at an even address, and resides in the address range 0 to FFFE<sub>16</sub>.

- **INTBASE** Interrupt Base Register The INTBASE register holds the address of the dispatch table for interrupts and traps. Refer to Chapter 3, "EX-CEPTIONS" for more information. The least significant bit and the two most significant bits of this register are always 0. Thus the dispatch table always starts at an even address, and resides in the address range 0 to FFFE<sub>16</sub>.

#### 2.3.3 The Processor Status Register

The Processor Status Register (PSR) holds status information and selects operating modes for the CR16A. It is 16 bits wide. Figure 2-2 shows the format of the PSR.

CompactRISC CR16A Programmer's Reference Manual

| 15 12    | 11 |   |   | 8 | 7 |   |   |   |   |   |   | 0 |  |

|----------|----|---|---|---|---|---|---|---|---|---|---|---|--|

| reserved | I  | Р | Е | 0 | Ν | Ζ | F | 0 | 0 | L | Т | С |  |

#### Figure 2-2. Processor Status Register

At reset, bits 0 through 11 of the PSR are cleared to 0, except for the PSR.E bit, which is set to 1. In addition, the value of each bit prior to reset is saved in the R1 general purpose register.

Several bits in the PSR have a dedicated condition code in the Conditional Branch (**Bcond**) instruction. These bits are Z, C, L, N, and F. Any Bcond instruction can cause a branch in the program execution, basd on the value of one of these PSR bits, or a combination of them. For example, one of the **Bcond** instructions, **BEQ** (Branch EQual), causes a branch if the PSR.Z flag is set. Refer to the **Bcond** instruction in "Instruction Definitions" on page 5-1 for details.

Bits 3, 4 and 8 have a constant value of 0. Bits 12 through 15 of the PSR register are reserved. The other bits are described below:

- **The C Bit** The Carry bit indicates whether a carry or borrow occurred after addition or subtraction. It can be used with the **ADDC** and **SUBC** instructions to perform multiple-precision integer arithmetic calculations. It is cleared to 0 if no carry or borrow occurred, and set to 1 if a carry or borrow occurred.

- **The T Bit** The Trace bit causes program tracing. While the T bit is set to 1, a Trace (TRC) trap is executed after every instruction. Refer to "Instruction Tracing" on page 4-1 for more information on program tracing. The T bit is automatically cleared to 0, when a trap or an interrupt occurs. The T bit is used in conjunction with the P bit, see below.

- **The L Bit** The Low flag is set by comparison operations. In integer comparison, the L flag is set to 1, if the second operand (Rdest) is less than the first operand (Rsrc) when both operands are interpreted as unsigned integers. Otherwise, it is cleared to 0. Refer to the specific compare instruction in "Instruction Definitions" on page 5-1 for details.

- **The F Bit** The Flag bit is a general condition flag which is set by various instructions. It may be used to signal exceptional conditions or to distinguish the results of an instruction (e.g., integer arithmetic instructions use it to indicate overflow from addition or subtraction). In addition it is set, or cleared, as a result of a Test-Bit instruction.

- The Z BitThe Zero bit is set by comparison operations. In integer comparisons it<br/>is set to 1 if the two operands are equal. Otherwise, it is cleared to 0.<br/>Refer to the specific compare instruction in "Instruction Definitions" on<br/>page 5-1 for details.

CompactRISC CR16A Programmer's Reference Manual

- **The N Bit** The Negative bit is set by comparison operations. In integer comparison it is set to 1 if the second operand (Rdest) is less than the first operand (Rsrc) when both operands are interpreted as signed integers. Otherwise it is cleared to 0. Refer to the specific compare instruction in "Instruction Definitions" on page 5-1 for details.

- **The E Bit** The local maskable interrupt Enable bit affects the state of maskable interrupts. While this bit and the PSR.I bit are 1, all maskable interrupts are accepted. While this bit is 0, only the non-maskable interrupt is accepted. On reset the E bit is set to 1. See "Interrupt Handling" on page 3-3.

There are two dedicated instructions that set and clear the E bit. It is set to 1 by the Enable Interrupts instruction (EI). It is cleared to 0 by the Disable Interrupts instruction (DI). This pair can be used to locally disable maskable interrupts, regardless of the global state of maskable interrupts, which is determined by the value of the PSR.I bit.

See also "Interrupt Handling" on page 3-3.

- **The P Bit** The Trace (TRC) trap Pending bit is used together with the T bit to prevent a TRC trap from occurring more than once for any instruction. It may be cleared to 0 (no TRC trap pending) or 1 (TRC trap pending). See "Exception Service Procedures" on page 3-6 and "Instruction Tracing" on page 4-1 for more information.

- **The l Bit** The global maskable Interrupt enable bit affects the state of maskable interrupts. While this bit and the PSR.E bits are 1, all maskable interrupts are accepted. While this bit is 0, only the non-maskable interrupt is accepted. The I bit is cleared to 0 on reset. In addition, it is automatically cleared when an interrupt occurs.

#### 2.3.4 The Configuration Register

The Configuration Register (CFG) is used to enable or disable various operating modes and to control optional on-chip caches in some cores that are based on the CompactRISC technology. The CR16A does not support any optional modules, and all the bits of the CFG register are reserved.

Figure 2-3 shows the format of the CFG register.

| 15 0     |  |

|----------|--|

| reserved |  |

Figure 2-3. Configuration Register

CompactRISC CR16A Programmer's Reference Manual

#### 2.4 MEMORY ORGANIZATION

The CR16A implements 18-bit addresses. This allows the CPU to access up to 256 Kbytes of data, and 128 Kbytes of program memory. The memory is a uniform linear address space. Memory locations are numbered sequentially starting at 0 and ending at  $2^{18}$ -1. The number specifying a memory location is called an address.

The contents of each memory location is a byte consisting of eight bits. Instructions and data can occupy any byte address in the range of 0 through 128 Kbyte and 256 Kbyte respectively, except for addresses  $0FC00_{16}$  through  $0FFF_{16}$  which are reserved, (see Figure 2-4).

Figure 2-4. Memory Organization

#### 2.4.1 Data References

Bit and byte order for data references The CR16A refers to bytes, and words, of data in memory. When it refers to a byte of data in memory, the data is actually located at the specified address. When it refers to a word of data in memory, the data is located at consecutive bytes beginning with the byte at the specified address.

The byte order in the CR16A is from least significant to most significant byte (little-endian). The address of a word of data refers to the least significant byte of the data value; the remaining byte is located at a higher address.

Bits are ordered from least significant to most significant. The least significant bit is in position zero. The **TBIT** instruction refers to bits by their ordinal position numbers. Figure 2-5 shows the memory representation for data values.

Figure 2-5. Data Representation

**Data references** The CR16A supports references to memory by the load and store instructions. Bytes, and words can be referenced on any boundary.

#### 2.4.2 Stacks

A *stack* is a one-dimensional data structure in which values are entered and removed, one item at a time, at one end called the *top-of-stack*. It consists of a block of memory and a variable called the *stack pointer*. Stacks are important data structures in both systems and applications programming. They are used to store status information during subroutine calls and interrupt servicing. Also, algorithms for expression evaluation in compilers and interpreters depend on stacks to store intermediate results. High level languages, such as C, keep local data and other information on a stack.

CompactRISC CR16A Programmer's Reference Manual

The CR16A provides support for two kinds of stacks: the interrupt stack and the program stack.

The interrupt stack The processor uses the interrupt stack to save and restore the program state during the handling of an exception condition. This information is automatically pushed, by the hardware, on to the interrupt stack before entering an exception service procedure. On exit from the exception service procedure, the hardware pops this information from the interrupt stack. See Chapter 3, "EXCEPTIONS" for more information on this subject. The interrupt stack can reside in the first 64 Kbyte of the address range, and is accessed via the ISP processor register.

The programThe program stack is normally used by programs at run time, to save<br/>and restore register values upon procedure entry and exit. It is also<br/>used to store local and temporary variables. The program stack is ac-<br/>cessed via the SP general-purpose register, and therefore must reside in<br/>the first 64 Kbyte of the address range. Note that this stack is handled<br/>by software only, e.g., the CompactRISC C Compiler generates code that<br/>pushes data on to, and pops data from, the program stack.

Both stacks expand downward in memory, toward address zero.

### 2.5 ADDRESSING MODES

Most instructions use one, two or three of the CR16A's registers as operands. Some instructions may also use an immediate value instead of the first register operand. Memory is accessed only by the load and store instructions, which use absolute, relative or far-relative addressing mode.

The following addressing modes are available:

**Register mode** In register mode, the operand is located in a general purpose register, i.e., R0 through R13, RA or SP. The following instruction illustrates register addressing mode.

ADDB R1, R2

ImmediateIn immediate mode, the operand is a constant value which is specifiedmodewithin the instruction. For example:

#### MULW \$4, R4

**PC-Relative**In PC-Relative mode, the operand is a displacement from the currentmodevalue of the PC register. For example:

BR \*+10

CompactRISC CR16A Programmer's Reference Manual

**Relative mode** In relative mode, the operand is located in memory. Its address is obtained by adding the contents of a general purpose register to the constant value in the displacement field encoded in the instruction. The following instruction illustrates relative addressing mode.

LOADW 12(R5), R6

**Far-relative** In far-relative mode, the operand is located in memory. Its address is obtained by concatenating a pair of adjacent general purpose registers to form an 18-bit value, and adding this value to the constant value in the displacement field encoded in the instruction.

The 16 least significant bits of the 18-bit value are taken from the base register, and the two most significant bits of the value are taken from the two least significant bits in the next consecutive register. The following instruction illustrates far-relative addressing mode.

STORW R7, 4(R3, R2)

**Absolute mode** In absolute mode, the operand is located in memory and its address is specified within the instruction. The following example illustrates absolute addressing mode.

LOADB 4000, R6

CompactRISC CR16A Programmer's Reference Manual

## Chapter 3 EXCEPTIONS

#### 3.1 INTRODUCTION

Program *exceptions* are conditions which alter the normal sequence of instruction execution, causing the processor to suspend the current process, and execute a special service procedure, often called a handler.

**Interrupts** An exception resulting from the activity of a source external to the processor is known as an *interrupt*; an exception which is initiated by some action or condition in the program itself is called a *trap*. Thus, an interrupt need have no relationship to the executing program, while a trap is caused by the executing program and will recur each time the program is executed. The CR16A recognizes nine exceptions: six traps and three types of interrupts.

The exception handling technique employed by an interrupt-driven processor determines how fast the processor can perform input/output transfers, the speed with which transfers between tasks and processes can be achieved, and the software overhead required for both. Therefore, it determines to a large extent the efficiency of a processor's multiprogramming and multitasking (including real-time) capabilities.

Addressing Exception handling in the CR16A uses a Dispatch Table in the first 64interrupts Kbyte of the memory whose base address is contained in the Interrupt Base register (INTBASE). See Figure 3-1.

Figure 3-1. Dispatch Table

For purposes of addressing the Dispatch Table, each of the exceptions has been assigned a number. This exception number (or interrupt vector) is used to compute the starting address of the service procedure for the particular exception required, i.e., the exception number is multiplied by two, and added to the contents of the Interrupt Base register (INTBASE). The resulting value matches the entry in the Dispatch Table that provides bits 1 through 16 of the address of the exception service procedure. The processor reconstructs the full address of the exception service procedure using the fact that its LSB (as is the LSB of any CR16A instruction address) is always 0.

**The interrupt process** When an exception occurs, the CPU automatically preserves the complete machine state of the program immediately prior to the occurrence of the exception. A copy of the PC and the PSR is made and pushed onto the Interrupt Stack. Depending on the kind of exception, it restores and/or adjust the contents of the Program Counter (PC) and the Processor Status Register (PSR). The interrupt exception number is then used to obtain the address of the exception service procedure from the dispatch table, which is then called.

The **RETX** instruction returns control to the interrupted program, and restores the contents of the PSR and the PC registers to their previous status. See the **RETX** instruction on page 5-28.

CompactRISC CR16A Programmer's Reference Manual

The following two subsections describe interrupts and traps in detail.

#### 3.1.1 Interrupt Handling

Interrupt handling in the CR16A provides a number of features which contribute to efficiency and programming flexibility. For example, rather than saving all registers when an interrupt occurs, the CR16A automatically saves only the Program Counter (PC) and the Program Status Register (PSR); the other registers are under program control. They may be saved and restored by the interrupt handlers. This provides a high degree of flexibility in adjusting interrupt response speed, and facilitates context switching for interrupts.

An Interrupt Stack allows context switching in a multiprogramming or multitasking environment without disabling interrupts.

The CR16A provides three types of interrupts: maskable interrupts, non-maskable interrupt (NMI) and In-System Emulator (ISE).

MaskableMaskable interrupts are disabled whenever PSR.E or PSR.I are cleared<br/>to 0. PSR.I serves as the global interrupt mask, while PSR.E serves as a<br/>local interrupt mask. PSR.E can be easily changed by using the EI and<br/>DI instructions (see the EI instruction on page 5-13 and the DI in-<br/>struction on page 5-12). PSR.E should be used when read-modify-write<br/>must be an atomic operations (i.e. no interrupt should occur between<br/>the read and the write).

Upon receipt of a maskable interrupt, the processor determines the vector number by performing an interrupt acknowledge bus cycle in which a byte is read from address  $0FE00_{16}$ . This byte contains a number in the range 16-127, which is used as an index into the Dispatch Table to find the address of the appropriate interrupt handler. Then, control is transferred to that interrupt handler.

- **Non-maskable** Non-maskable interrupts cannot be disabled; they occur when cata **interrupt** strophic events (such as an imminent power failure) require immediate handling to preserve system integrity. Non-maskable interrupts use vector number 1 in the Dispatch Table. When a non-maskable interrupt is detected, the CR16A performs an interrupt-acknowledge bus cycle to address 0FF00<sub>16</sub>, and discards the byte that is read during the bus cycle.

- **ISE interrupt** In-System Emulator (ISE) interrupts cannot be disabled; they temporarily suspend execution when an appropriate signal is activated. ISE interrupts use vector number 15 in the Dispatch Table. When an ISE interrupt is detected, the CR16A performs an interrupt-acknowledge bus cycle to address  $0FC00_{16}$ , and discards the byte that is read during the bus cycle.

CompactRISC CR16A Programmer's Reference Manual

#### 3.1.2 Traps

The CR16A recognizes the following traps:

- BPT Trap Breakpoint Trap Used for program debugging. Caused by the EXCP BPT instruction.

- **SVC Trap** Supervisor Call Trap Temporarily, transfers control to supervisor software, typically to access facilities provided by the operating system. Caused by the **EXCP SVC** instruction.

- **FLG Trap** Flag Trap Indicates various computational exceptional conditions. Caused by the **EXCP FLG** instruction.

- **DVZ Trap** Division by Zero Trap Indicates an integer division by zero. Caused by the **EXCP** DVZ instruction, which can be used by integer division emulation code to indicate this exception.

- **UND Trap** Undefined Instruction Trap Indicates undefined op codes. Caused by an **EXCP UND** instruction or an attempt to execute any of the following:

- any undefined instruction;

- the **EXCP** instruction when a reserved field in the dispatch table is specified.

- **TRC Trap** Trace Trap A TRC trap occurs before an instruction is executed when the PSR.P bit is 1. Used for program debugging and tracing. See Chapter 4, "ADDITIONAL TOPICS" for more information.

### 3.2 EXCEPTION PROCESSING

#### 3.2.1 Instruction Endings

The CR16A checks for exceptions at various points during the execution of instructions. Some exceptions, such as interrupts, are acknowledged between instructions, i.e., before the next instruction is executed. Other exceptions, such as a Division by Zero (DVZ) trap, are acknowledged during execution of an instruction. In such a case, the instruction is suspended. See Table 3-1.

When an instruction is suspended, it is not completed, but all other previously issued instructions have been completed. Result operands and flags (except for the PSR.P bit on some traps) are not affected. In this case, the PC saved on the interrupt stack contains the address of the suspended instruction.

CompactRISC CR16A Programmer's Reference Manual

When an interrupt is detected while a **MULi** instruction is being executed, the **MULi** instruction is suspended.

### 3.2.2 Acknowledging an Exception

The CR16A performs the following operations in response to interrupt or trap exceptions:

- 1. Decrements the Interrupt Stack Pointer (ISP) by 4.

- 2. Saves the contents of the current PSR and of the current value of bits 1 through 16 of the PC on the interrupt stack. See Figure 3-2. The contents of the PSR are located at the higher address.

- 3. Alters the PSR by clearing certain control bits. See Table 3-1.

- 4. For interrupts, displays information during the interrupt acknowledge bus cycle to indicate the type of interrupt encountered. If the interrupt is a maskable interrupt, the CPU reads the vector number during this cycle from address FE00<sub>16</sub>, that is mapped to the Interrupt Control Unit (ICU). If the interrupt is a Non Maskable Interrupt (NMI) the CPU performs

If the interrupt is a Non Maskable interrupt (NMI) the CPU performs a read operation from address  $FF00_{16}$  for observability purposes. If the interrupt is an ISE interrupt the CPU also performs a read operation from address  $FC00_{16}$  for observability purposes.

5. Reads the word entry from the dispatch table at address (INTBASE) + vector X 2. The dispatch table entry is used to call the exception service procedure and is interpreted as a pointer that is loaded into bits 1 through 16 of the PC. Bits 0 and 17 of the PC are cleared. See Figure 3-3.

Figure 3-2. Saving the PC and PSR Contents During an Exception Acknowledge Sequence

Figure 3-3. Transfer of Control During an Exception Acknowledge Sequence

Table 3-1 summarizes how each type of exception is acknowledged.

| Table 3-1. Summary of Exception Processin | ıg |

|-------------------------------------------|----|

|-------------------------------------------|----|

|                                    | Instruction                    | PC      | Cleared PSR Bits     |                     |  |  |

|------------------------------------|--------------------------------|---------|----------------------|---------------------|--|--|

| Exception                          | Completion<br>Status           | Saved   | Before<br>Saving PSR | After<br>Saving PSR |  |  |

| Interrupt                          | Before start of<br>instruction | Next    | None                 | IPT                 |  |  |

| Interrupt during execution of MUL1 | Suspended                      | Current | P <sup>a</sup>       | IPT                 |  |  |

| BPT, DVZ, FLG,<br>SVC              | Suspended                      | Current | None                 | РТ                  |  |  |

| UND                                | Suspended                      | Current | None                 | РТ                  |  |  |

| TRC                                | Before start of<br>instruction | Next    | Р                    | РТ                  |  |  |

a. The PSR.P bit is cleared when an interrupt is acknowledged before a **MULi** instruction is completed, to prevent a mid-instruction trace trap upon return from the exception service procedure.

## 3.2.3 Exception Service Procedures

After the CR16A acknowledges an exception, control is transferred to the appropriate exception service procedure. The TRC trap is disabled (the PSR.P and PSR.T bits are cleared). Maskable interrupts are also disabled (the PSR.I bit is cleared) for a service procedure called in response to an interrupt.

At the beginning of each instruction, the PSR.T bit is copied into the PSR.P. If PSR.P is still set at the end of the instruction, a TRC trap is executed before the next instruction.

To complete a suspended instruction, the exception service procedure should be programmed to do one of the following:

Simulate a suspended of the suspended instruction. After it calculates and writes the results of the suspended instruction, it should modify the flags in the copy of the PSR which were saved on the interrupt stack, and update the PC saved on the interrupt stack to point to the next instruction to be executed.

The exception service procedure can then execute the **RETX** instruction, and the CR16A will begin executing the instruction following the suspended instruction. For example, when an Undefined Instruction Trap (UND) occurs, software can be used to perform the appropriate corrective actions.

**Retry execution** The suspended instruction can be retried after the exception service **of a suspended** procedure has corrected the trap condition that caused the suspension. **instruction**

In this case, the exception service procedure should execute the **RETX** instruction at its conclusion; then the CR16A will retry the suspended instruction. A debugger takes this action when it encounters an **EXCP BPT** instruction that was temporarily placed in another instruction's location in order to set a breakpoint. In this case, exception service procedures should clear the PSR.P bit to prevent a TRC trap from occurring again.

#### 3.2.4 Returning From Exception Service Procedures

Service procedures perform actions appropriate for the type of exception detected. At their conclusion, service procedures execute the **RETX** instruction to resume executing instructions at the point where the exception was detected.

### 3.2.5 Priority Among Exceptions

The CR16A checks for specific exceptions at various points while executing an instruction (see Figure 3-4).

If several exceptions occur simultaneously, the CR16A responds to the exception with the highest priority.

If several maskable interrupts occur simultaneously, the Interrupt Control Unit (ICU) determines the highest priority interrupt, and requests the CR16A to service this interrupt.

CompactRISC CR16A Programmer's Reference Manual

Figure 3-4. Exception Processing Flowchart

Before executing an instruction

Before executing an instruction, the CR16A checks for pending interrupts and trace traps, in that order. It responds to the interrupts in order of descending priority (i.e., first non-maskable interrupts, then maskable interrupts and lastly, ISE interrupts.

If no interrupt is pending, and PSR.P is 1 (i.e., a trace trap is pending), then the CR16A clears PSR.P and processes the trace trap.

CompactRISC CR16A Programmer's Reference Manual

If no trace trap or interrupt is pending, then the CR16A begins executing the instruction by copying PSR.T to PSR.P. While executing an instruction, the CR16A may detect a trap.

DuringFirst, the CR16A checks for an undefined instruction (UND) trap; thenexecution of anit looks for any of the following mutually exclusive traps: SVC, DVZ,instructionFLG or BPT. The CR16A responds to the first trap it detects by suspending the current instruction and executing the trap.

If an undefined instruction is detected, then no data references are performed for the instruction.

If an interrupt becomes pending during execution of the **MULi** instruction the CR16A clears PSR.P to 0 and responds to the requested interrupt.

If no exception is detected while the instruction is executing, then the instruction is completed (i.e., values are changed in registers and memory, except for PSR.P, which was changed earlier) and the PC is updated to point to the next instruction.

#### 3.2.6 Nested Interrupts

A nested interrupt is an interrupt that occurs while another interrupt is being serviced. Since the PSR.I bit is automatically cleared before any interrupt is serviced (see Table 3-1), nested maskable interrupts are not serviced by default. However, the Exception Service Procedure can explicitly allow nested maskable interrupts at any point, by setting the PSR.I bit using a LPR instruction. In this case, pending maskable interrupts are serviced normally even in the middle of the currently executing Exception Service Procedure.

It is possible to enable nesting of specific maskable interrupts inside a certain Exception Service Procedure. This is done by programming the Interrupt Control Unit (ICU) to mask the undesired interrupt sources, during the execution of the Exception Service Procedure. This should be done before the PSR.I bit is set.

Nested Non Maskable Interrupt (NMI) and nested ISE interrupt are always serviced.

The interrupt nesting level is limited only by the amount of memory that is available for the interrupt stack.

CompactRISC CR16A Programmer's Reference Manual

#### 3.3 RESET

A reset occurs when the appropriate signal is activated. Reset must be used at power-up to initialize the CR16A.

As a result of a reset operation:

- All instructions currently being executed are terminated.

- Results and flags normally affected by the terminated instruction are unpredictable.

- The results of instructions, whose execution started but did not yet end, may not be written to their destinations.

- Any pending interrupts and traps are eliminated.

Upon reset, the following operations are executed:

- 1. The current values of bits 1 through 16 of the PC are stored in R0, and the current value of the PSR is stored in R1.

- 2. The following internal registers are cleared to 0: PC, CFG and PSR, except for PSR.E, which is set to 1.

After reset, the processor begins normal execution at memory location 0, and the reserved bits in these registers, and the contents of all other registers, are unpredictable.

## Chapter 4 ADDITIONAL TOPICS

This chapter discusses debugging support and instruction execution order.

### 4.1 DEBUGGING SUPPORT

The CR16A provides the following features to make program debugging easier.

- Instruction Tracing

- Soft Break Generation by Breakpoint Instruction

- ISE Support

The PSR is used to control these features.

#### 4.1.1 Instruction Tracing

Instruction tracing can be used during debugging to single-step through selected portions of a program. The CR16A uses two bits in the PSR to enable and generate trace traps. Tracing is enabled by setting the T bit in the PSR register.

During the execution of each instruction, the CR16A copies the PSR.T bit into the PSR.P (trace pending) bit. Before beginning the next instruction, the CR16A checks the PSR.P bit to determine whether a Trace (TRC) trap is pending. If PSR.P is 1, i.e., a trace trap is pending, the CR16A generates a trace trap before executing the instruction.

If any other trap or interrupt is requested during execution of a traced instruction, its entire service procedure is allowed to complete before the TRC trap occurs.

For example, if an Undefined Instruction (UND) trap is detected while tracing is enabled, the TRC trap occurs after execution of the **RETX** instruction that marks the end of the UND service procedure. The UND service procedure can use the PC value saved on top of the interrupt stack to determine the location of the instruction. The UND service procedure is not affected, whether instruction tracing was enabled or not.

CompactRISC CR16A Programmer's Reference Manual

ADDITIONAL TOPICS 4-1

Each interrupt and trap sequence can update the PSR.P bit, when required for proper tracing. This guarantees only one TRC trap per instruction, and that the return address pushed during a TRC trap is always the address of the next instruction to be traced.

Note the following:

- LPR (on PSR) and **RETX** instructions cannot be reliably traced because they may alter the PSR.P bit during their execution.

- If instruction tracing is enabled while the **WAIT** instruction is executed, a trace trap occurs after the next interrupt, when the interrupt service procedure returns.

- **The Breakpoint** The breakpoint instruction (**EXCP BPT**) may be used by debuggers to **Instruction** stop the execution of a program at specified instructions, to examine the status of the program. The debugger replaces these instructions with the breakpoint instruction. It then starts the program execution. When such an instruction is reached, the breakpoint instruction causes a trap, which enables the debugger to examine the status of the program at that point.

#### 4.1.2 In-System Emulator (ISE) Support

The CR16A core provides the following to support the development of real-time In-System Emulator (ISE) equipment and Application Development Boards (ADBs).

- Status signals that indicate when an instruction in the execution pipeline is completed and the length of this instruction.

- Status signals that indicate the type of each bus cycle, e.g., fetch.

- Status signals that indicate when there is a non-sequential fetch.

- An ISE interrupt signal.

- An interrupt acknowledge cycle.

- A special bus status signal during exception handling, that indicates that the dispatch table is being read.

- Upon reset, the CR16A stores the contents of the PSR in R1 and the contents of bits 1 through 16 of the PC in R0.

ADDITIONAL TOPICS 4-2

### 4.2 INSTRUCTION EXECUTION ORDER

The CR16A has four operating states in which instructions may be executed and exceptions may be processed. They are:

- Reset

- Executing Instructions

- Processing Exception

- Waiting for Interrupt

These states and the transitions between them are shown in Figure 4-1.

Figure 4-1. CR16A Operating States

Reset When the reset input signal is activated, the CR16A enters the reset state. In the reset state, the contents of certain dedicated registers are initialized, as specified in "Reset" on page 3-10. Executing When the reset signal is deactivated the CR16A enters the executing-instructions state. In this state, the CR16A executes instructions repeat-Instructions edly until an exception is recognized or a WAIT instruction is executed. Processing When an exception is recognized the CR16A enters the processing ex-Exception ception state in which it saves the PC and the PSR contents. The processor then reads an absolute address from the Interrupt Dispatch Table and branches to the appropriate exception service procedure. Refer to "The interrupt process" on page 3-2 for more information. To process maskable interrupts, the CR16A also reads a vector value from an Interrupt Control Unit (ICU).

CompactRISC CR16A Programmer's Reference Manual

ADDITIONAL TOPICS 4-3

After successfully completing all data references required to process an exception, the CR16A reverts to the executing instructions state.

Waiting for<br/>InterruptWhen a WAIT instruction is executed, the CR16A enters the wait for in-<br/>terrupt state in which it is idle. When an interrupt is detected the pro-<br/>cessor enters the processing exception state.

### 4.2.1 The Instruction Pipeline

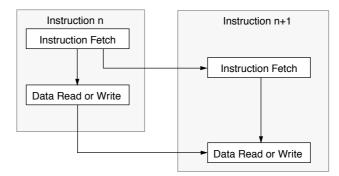

The operations for each instruction are not necessarily completed before the operations of the next instruction begin. The CR16A can overlap operations for several instructions, using a pipelined technique to enhance its performance. While the CR16A is fetching one instruction, it can simultaneously be decoding a second instruction and calculating results for a third instruction. See Figure 4-2.

In most cases, pipelined instruction execution improves performance while producing the same results as strict sequential instruction execution. Under certain circumstances, however, the effects of this performance enhancement are visible to system software and hardware as differences in the order of memory references performed by the CR16A. See explanation below.

InstructionThe CR16A fetches an instruction only after all previous instructionsFetcheshave been completely fetched. But, it may begin fetching the instruction<br/>before all of the source operands have been read, and before results<br/>have been written for previous instructions.

Operands and<br/>MemoryThe source operands for an instruction are read only after all data<br/>reads, and data writes in previous instructions have been completed.<br/>This process and the order of precedence of memory reference for two<br/>consecutive instructions is illustrated in Figure 4-2. The arrows indicate<br/>order of precedence between operations in an instruction and between<br/>instructions.

ADDITIONAL TOPICS 4-4

### Figure 4-2. Memory References for Consecutive Instructions

Overlapping<br/>OperationsAs a consequence of overlapping the operations for several instructions,<br/>the CR16A may fetch an instruction, but not execute it (for example, if<br/>the previous instruction causes a trap). The CR16A reads source oper-<br/>ands and writes destination operands for executed instructions only.

**Dependencies** The CR16A does not check for dependencies between the fetching of the next instruction and the writing of the results of the previous instructions. Therefore, special care is required when executing self-modifying code.

### 4.2.2 Serializing Operations

The CR16A serializes instruction execution after processing an exception. This means that it finishes writing all the results of the preceding instructions to a destination, before it fetches the next instruction. This fetch is non-sequential.

The CR16A also serializes instruction execution after executing the following instructions: LPR, RETX, and EXCP.

CompactRISC CR16A Programmer's Reference Manual

ADDITIONAL TOPICS 4-5

# Chapter 5 INSTRUCTION SET

This chapter describes each of the CR16A instructions, in detail.

### 5.1 INSTRUCTION DEFINITIONS

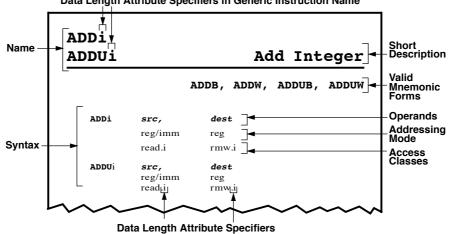

The name of each operand appears in bold italics, and indicates its use. In addition, the valid addressing modes, access class and length are specified for each operand. The addressing mode may be: *reg* (register), *procreg* (processor register), *imm* (immediate), *abs* (absolute), *rel* (relative) or *far* (far relative). The access class may be *read*, *write*, *rmw* (read-modify-write), *addr* (address) or *disp* (displacement). The access class is followed by a data length attribute specifier. See Figure 5-1.

Data Length Attribute Specifiers in Generic Instruction Name

Figure 5-1. Instruction Header Format

The data length attribute specifier specifies how the operands will be interpreted, and represents a character that is incorporated into the name of the actual instruction. The  $\mathbf{i}$  specifier stands for a **B** (byte) or **W** (word) in the actual instruction name.

CompactRISC CR16A Programmer's Reference Manual

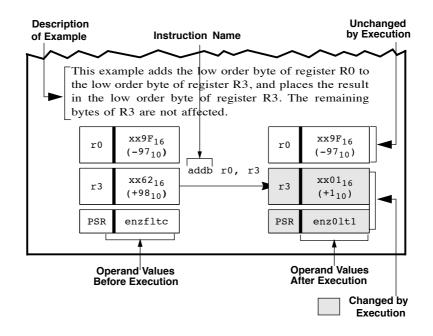

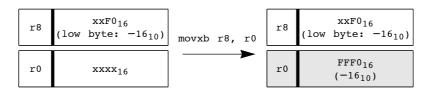

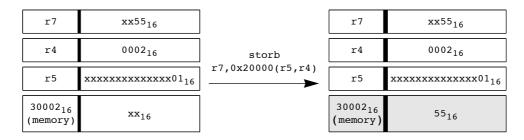

Each instruction definition is followed by a detailed example of one or more typical forms of the instruction. In each example, all the operands of the instruction are identified, both those explicitly stated in assembly language and those that will be implicitly affected by the instruction.

For each example, the values of operands before and after execution of the instruction are shown. Often the value of an operand is not changed by the instruction. When the value of an operand changes, it's field is highlighted, i.e., its box is grey. See Figure 5-2.

Figure 5-2. Instruction Example Format

The least significant digit of the least significant byte is the rightmost digit. Values are expressed in terms of a radix in a subscript to the value.

An  $\mathbf{x}$  represents a binary digit or a hexadecimal digit (4 bits) that is either ignored or unchanged.

### 5.2 DETAILED INSTRUCTION LIST

The following pages describe in detail the instruction set.

CompactRISC CR16A Programmer's Reference Manual

### ADDi ADDUi

# Add Integer

ADDB, ADDW, ADDUB, ADDUW

| ADDi  | src,                    | dest               |

|-------|-------------------------|--------------------|

|       | reg/imm                 | reg                |

|       | read.i                  | rmw.i              |

|       |                         |                    |

| ADDUi | src,                    | dest               |

| ADDUİ | <i>src</i> ,<br>reg/imm | <b>dest</b><br>reg |

The **ADDi** and **ADDUi** instructions add the *src* and *dest* operands, and place the result in the *dest* operand.

**Flags:** During execution of an **ADDi** instruction, PSR.C is set to 1 on a carry from addition, and cleared to 0 if there is no carry. PSR.F is set to 1 on an overflow from addition, and cleared to 0 if there is no overflow. PSR flags are not affected by the **ADDUi** instruction.

Traps: None

**Example:** This example adds the low order byte of register R0 to the low order byte of register R3, and places the result in the low order byte of register R3. The remaining bytes of R3 are not affected.

| r0  | xx9F <sub>16</sub><br>(-97 <sub>10</sub> ) |             | r0  | xx9F <sub>16</sub><br>(-97 <sub>10</sub> ) |

|-----|--------------------------------------------|-------------|-----|--------------------------------------------|

| r3  | xx62 <sub>16</sub><br>(+98 <sub>10</sub> ) | addb r0, r3 | r3  | $xx01_{16}$<br>(+1 <sub>10</sub> )         |

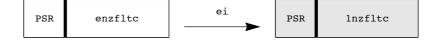

| PSR | enzfltc                                    |             | PSR | enz0lt1                                    |

# Add Integer with Carry

### ADDCB, ADDCW

| ADDCi | <b>src</b> , | dest  |

|-------|--------------|-------|

|       | reg/imm      | reg   |

|       | read.i       | rmw.i |

The **ADDCi** instructions add the *src* operand *dest* operand and the PSR.C flag, and places the sum in the *dest* operand.

Flags: PSR.C is set to 1 if a carry occurs, and cleared to 0 if there is no carry. PSR.F is set to 1 if an overflow occurs, and cleared to 0 if there is no overflow.

Traps: None

Examples: 1. Example 1 adds 32, the low order byte of register R0, and the PSR.C flag contents and places the result in the low order byte of register R0. The remaining bytes of register R0 are unaffected.

| r0  | xx0F <sub>16</sub><br>(+15 <sub>10</sub> ) | addcb \$32, r0 | r0  | xx30 <sub>16</sub><br>(+48 <sub>10</sub> ) |

|-----|--------------------------------------------|----------------|-----|--------------------------------------------|

| PSR | enzflt1                                    |                | PSR | enz0lt0                                    |

2. Example 2 adds the contents of registers R5 and R0, and the contents of the PSR.C flag, and places the result in register R0.

| r5  | FFFF <sub>16</sub><br>(-1 <sub>10</sub> )  |              | r5  | FFFF <sub>16</sub><br>(-1 <sub>10</sub> )  |

|-----|--------------------------------------------|--------------|-----|--------------------------------------------|

| r0  | 0030 <sub>16</sub><br>(+48 <sub>10</sub> ) | addcw r5, r0 | r0  | 0030 <sub>16</sub><br>(+48 <sub>10</sub> ) |

| PSR | enzflt1                                    |              | PSR | enz0lt1                                    |

### CompactRISC CR16A Programmer's Reference Manual

# ANDi

# **Bitwise Logical AND**

### ANDB, ANDW

| ANDi | <b>src</b> , | dest  |

|------|--------------|-------|

|      | reg/imm      | reg   |

|      | read.i       | rmw.i |

The **ANDi** instructions perform a bitwise logical AND operation on the *src* and dest operands, and places the result in the *dest* operand.

Flags:

Example:

Traps:

None

None

This example ANDs the low order bytes of registers R0 and R11 and places the result in the low order byte of register R11. The remaining byte of register R11 is unaffected.

| r0  | xx <sub>16</sub> | 100100102 | andb r0, r11 | r0  | xx <sub>16</sub> | 100100102 |

|-----|------------------|-----------|--------------|-----|------------------|-----------|

| r11 | xx <sub>16</sub> | 011101112 |              | r11 | xx <sub>16</sub> | 000100102 |

## Arithmetic Shift

### ASHUB, ASHUW

| ASHUİ | count,  | dest  |

|-------|---------|-------|

|       | reg/imm | reg   |

|       | read.B  | rmw.i |

The **ASHUI** instructions perform an arithmetic shift on the **dest** operand as specified by the **count** operand. Both operands are interpreted as signed integers.

The sign of **count** determines the direction of the shift. A positive **count** specifies a shift to the left; a negative **count** specifies a shift to the right. The absolute value of the **count** specifies the number of bit positions to shift the **dest** operand. The **count** operand value must be in the range -7 to +7 if **ASHUB** is used; and in the range -15 to +15 if **ASHUW** is used. Otherwise, the result is unpredictable.

If the shift is to the left, high order bits (including the sign bit) shifted out of **dest** are lost, and low order bits emptied by the shift are filled with zeros. If the shift is to the right, low order bits shifted out of **dest** are lost, and high order bits emptied by the shift are filled from the original sign bit of **dest**.

Flags: None

Traps: None

**Examples:** 1. Example 1 shifts the low order byte of register R5 two bit positions to the left. The remaining byte of register R5 is unaffected.

| r5 | xx <sub>16</sub> | 00011111 <sub>2</sub> | ashub \$2, r5<br> | r5 | xx <sub>16</sub> | 01111100 <sub>2</sub> |

|----|------------------|-----------------------|-------------------|----|------------------|-----------------------|

|----|------------------|-----------------------|-------------------|----|------------------|-----------------------|

2. Example 2 reads a byte from register R4. Based on this value, it shifts the low order byte of register R6 accordingly. The remaining byte of register R6 is unaffected.

| r4 | xx <sub>16</sub> | 11111110 <sub>2</sub><br>(-2 <sub>10</sub> ) | ashub r4, r6 | r4 | xx <sub>16</sub> | $(-2_{10})$           |

|----|------------------|----------------------------------------------|--------------|----|------------------|-----------------------|

| r6 | xx <sub>16</sub> | 11111000 <sub>2</sub>                        |              | r6 | xx <sub>16</sub> | 11111110 <sub>2</sub> |

CompactRISC CR16A Programmer's Reference Manual

BEQ, BNE, BCS, BCC, BHI, BLS, BGT, BLE, BFS, BFC, BLO, BHS, BLT, BGE

Bcond dest imm disp

If the condition specified by **cond** is true, the **Bcond** instruction causes a branch in program execution. Program execution continues at the location specified by **dest**, sign extended to 18 bits, plus the current contents of the Program Counter. Both the least significant bit and the most significant bit of the address are cleared to 0. If the condition is false, execution continues with the next sequential instruction.

**cond** is a two-character condition code that describes the state of a flag or flags in the PSR. If the flag(s) are set as required by the specified **cond**, the condition is true; otherwise, the condition is false. The following table describes the possible **cond** codes and the related PSR flag settings:

| cond Code | Condition             | True State          |  |

|-----------|-----------------------|---------------------|--|

| EQ        | Equal                 | Z flag is 1         |  |

| NE        | Not Equal             | Z flag is 0         |  |

| CS        | Carry Set             | C flag is 1         |  |

| СС        | Carry Clear           | C flag is 0         |  |

| н         | Higher                | L flag is 1         |  |

| LS        | Lower or Same         | L flag is 0         |  |

| GT        | Greater Than          | N flag is 1         |  |

| LE        | Less Than or Equal    | N flag is 0         |  |

| FS        | Flag Set              | F flag is 1         |  |

| FC        | Flag Clear            | F flag is 0         |  |

| LO        | Lower                 | Z and L flags are 0 |  |

| HS        | Higher or Same        | Z or L flag is 1    |  |

| LT        | Less Than             | Z and N flags are 0 |  |

| GE        | Greater Than or Equal | Z or N flag is 1    |  |

Flags:

Traps:

CompactRISC CR16A Programmer's Reference Manual

None

None

### Examples:

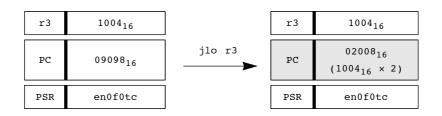

1. Example 1 passes execution control to the instruction labeled LOOP by adding 1FF68<sub>16</sub> to the PC, if the PSR.Z and PSR.L flags are 0.

| PC                            | 09098 <sub>16</sub> |          | PC                            | 09000 <sub>16</sub> |

|-------------------------------|---------------------|----------|-------------------------------|---------------------|

| LOOP<br>(9000 <sub>16</sub> ) | xxxx <sub>16</sub>  | blo LOOP | LOOP<br>(9000 <sub>16</sub> ) | xxxx <sub>16</sub>  |

| PSR                           | en0f0tc             | ]        | PSR                           | en0f0tc             |

2. Example 2 passes execution control to a non-sequential instruction if the PSR.Z flag is 0. The instruction passes execution control by adding 16 to the PC register.

| PC                            | 09FF0 <sub>16</sub><br>(40944 <sub>10</sub> ) |          | PC                            | 0A000 <sub>16</sub><br>(40960 <sub>10</sub> ) |

|-------------------------------|-----------------------------------------------|----------|-------------------------------|-----------------------------------------------|

| *+16<br>(A000 <sub>16</sub> ) | xxxx <sub>16</sub>                            | bne *+16 | *+16<br>(A000 <sub>16</sub> ) | xxxx <sub>16</sub>                            |

| PSR                           | en0fltc                                       |          | PSR                           | en0fltc                                       |

BAL

| BAL | link,   | dest |

|-----|---------|------|

|     | reg     | imm  |

|     | write.W | disp |

The address of the next sequential instruction is first stored in the register specified as the *link* operand. Then, program execution continues at the address specified by **dest**, sign extended to 18 bits, plus the current contents of the PC register. Both the least significant bit and the most significant bit of the address are cleared to 0.

Flags: None

None

Traps:

**Example:** This example saves bits 1 through 16 of the PC of the next sequential instruction in register RA, and passes execution control to the instruction labeled L by adding  $00F6C_{16}$  to the current PC.

| PC                         | 09098 <sub>16</sub><br>(37016 <sub>10</sub> ) |           | PC                         | 0A004 <sub>16</sub><br>(40964 <sub>10</sub> )   |

|----------------------------|-----------------------------------------------|-----------|----------------------------|-------------------------------------------------|

| L<br>(A004 <sub>16</sub> ) | xxxx <sub>16</sub>                            | bal ra, L | L<br>(A004 <sub>16</sub> ) | xxxx <sub>16</sub>                              |

| ra                         | xxxx <sub>16</sub>                            |           | ra                         | 0484E <sub>16</sub><br>(37020 <sub>10</sub> ÷2) |

CompactRISC CR16A Programmer's Reference Manual

BR