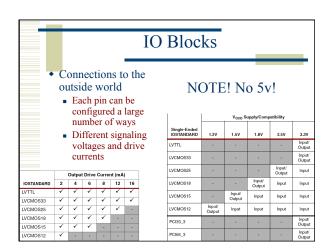

| ΙΟ                                                                            | Bloc         | ks               |                  | _                |                  |                  |

|-------------------------------------------------------------------------------|--------------|------------------|------------------|------------------|------------------|------------------|

| <ul> <li>Connections to the outside world</li> <li>Each pin can be</li> </ul> | 1            | I                | V S              | upply/Comp       | artibility       |                  |

| configured a large<br>number of ways                                          | Single-Ended | 1.2V             | 1.5V             | 1.8V             | 2.5V             | 3.3V             |

|                                                                               | LVTTL        | -                | -                | •                |                  | Input/<br>Output |

| <ul> <li>Different signaling</li> </ul>                                       | LVCMOS33     |                  |                  |                  |                  | Input/<br>Output |

| voltages and drive                                                            | LVCMOS25     |                  |                  |                  | Input/<br>Output | Input            |

| currents                                                                      | LVCMOS18     |                  |                  | Input/<br>Output | Input            | Input            |

|                                                                               | LVCMOS15     |                  | Input/<br>Output | Input            | Input            | Input            |

|                                                                               | LVCMOS12     | Input/<br>Output | Input            | Input            | Input            | Input            |

|                                                                               | PCI33_3      |                  | •                | •                |                  | Input/<br>Output |

| CS/EE 3710                                                                    | PCI66_3      |                  |                  |                  |                  | Input/<br>Output |

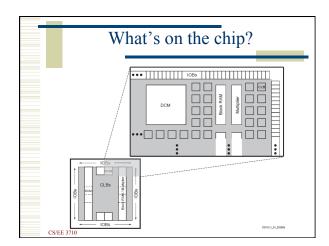

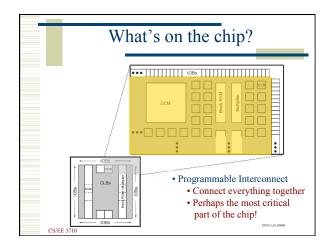

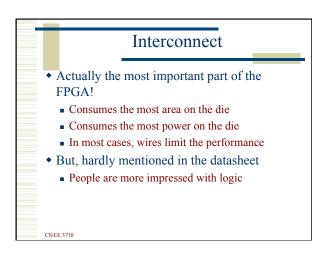

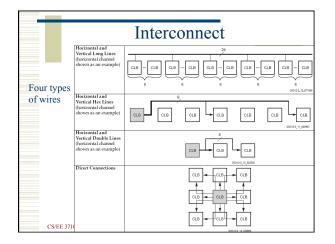

|      |               | Inte | rconn                  | ect                  |                  |

|------|---------------|------|------------------------|----------------------|------------------|

| on-c | chip netw     |      |                        |                      |                  |

| Swi  |               |      | Switch<br>Aatrix - IOB |                      |                  |

| Swi  | itch<br>ttrix |      | Switch - CLB           | Switch<br>Matrix CLB | Switch<br>Matrix |

|      | itch<br>ttrix |      | witch<br>Aatrix CLB    | Switch<br>Matrix CLB | Switch<br>Matrix |

| Swi  |               |      | Switch<br>Matrix CLB   | Switch<br>Matrix CLB | Switch<br>Matrix |

| Swi  | itch<br>ttrix |      | Switch<br>Aatrix CLB   | Switch<br>Matrix CLB | Switch<br>Matrix |

|      |               |      |                        |                      | D5312_09_009905  |

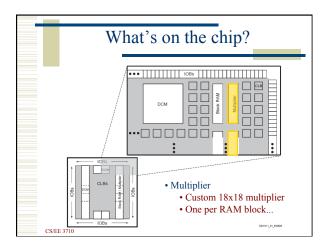

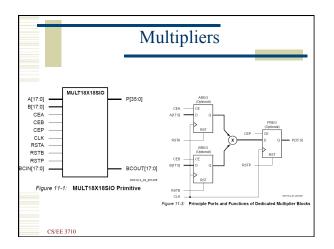

| Multipliers                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>module mult18x18sio(a,b,clk,prod);<br/>input [7:0] a;<br/>input [7:0] b;<br/>input clk;<br/>output [15:0] prod;<br/>reg [15:0] prod;<br/>always @(posedge clk) prod &lt;= a*b;<br/>endmodule</pre> |

| CS/EE 3710                                                                                                                                                                                              |

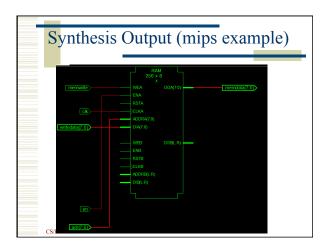

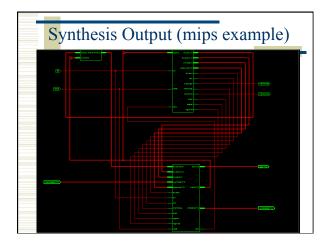

|                                                | Device Utilization Summar |           |             |

|------------------------------------------------|---------------------------|-----------|-------------|

| Logic Utilization                              | Used                      | Available | Utilization |

| Number of Slice Flip Flops                     | 79                        | 9,312     | 1%          |

| Number of 4 input LUTs                         | 193                       | 9,312     | 2%          |

| Logic Distribution                             |                           |           |             |

| Number of occupied Slices                      | 123                       | 4,656     | 2%          |

| Number of Slices containing only related logic | 123                       | 123       | 100%        |

| Number of Slices containing unrelated logic    | 0                         | 123       | 0%          |

| Total Number of 4 input LUTs                   | 193                       | 9,312     | 2%          |

| Number used as logic                           | 161                       |           |             |

| Number used for Dual Port RAMs                 | 32                        |           |             |

| Number of bonded IOBs                          |                           |           |             |

| Number of bonded                               | 19                        | 232       | 8%          |

| Number of RAMB16s                              | 1                         | 20        | 5%          |

| Number of BUFGMUXs                             | 1                         | 24        | 4%          |

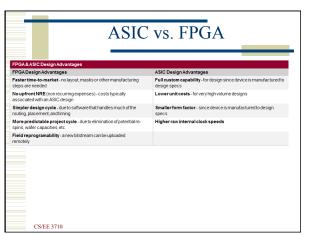

FPGAs consume more power

CS/EE 3710

- FPGAs are bigger for the same function

- ASICs are *much* more expensive to develop

NRE Non-Recurring Engineering