# **Tutorial: Xilinx ISE 14.4 and Digilent Nexys 3**

#### This tutorial will show you how to:

- Part I: Set up a new project in ISE 14.4

- Part II: Implement a function using Schematics

- Part III: Implement a function using Verilog HDL

- Part IV: Simulate the schematic/Verilog circuit using the ISim + Verilog test fixture

- Part V: Constraint, Synthesize, Implement, Generate, and Program for Nexys 3 FPGA board

I assume that you're using a DSL lab machine, or that you've installed Xilinx ISE 14.4 on your own machine as some of the following procedures may be different depending on the version of ISE.

# Part I: Set up a new project in ISE 14.4

Attention: Make sure to use the appropriate version of the ISE, 64 bit navigator for a 64 bit OS, and 32 bit for 32 bit. If you don't pay attention to this, there will be unexpected behavior in the ISE software and thing may not work properly!

1. Open the Xilinx ISE Design Suit 14.4. You can click on the ISE icon on the desktop, or search Start → All Programs → Xilinx ISE Design Suite 14.4 → ISE Design Tools → Project Navigator

The screen should look something like the following, the ISE always defaults to the last open project unless none where open before just like the following:

|                                                                                                                                  | - 0 × |

|----------------------------------------------------------------------------------------------------------------------------------|-------|

| Edit View Project Source Process Jools Window Layout Help                                                                        |       |

| ■ 2 2 2 4 2 4 2 4 2 4 2 4 2 4 2 4 2 4 2                                                                                          |       |

| + 5 Z X                                                                                                                          |       |

| • C B X   ekone to E SQ @ Design Suite   endered   endered   endered   endered   endered   endered   endered   endered   endered |       |

|                                                                                                                                  |       |

|                                                                                                                                  | ⇔⊡ē×  |

|                                                                                                                                  | *     |

| mode 🙆 Errors 🔔 Warmops 🙀 Fricin Files Results                                                                                   |       |

2. Now either press the New Project tab or select File  $\rightarrow$  New Project... and change the Name and Location to whatever you like.

Attention: Xilinx does not allow spaces in path or file names! For example "C:\ECE 3700 will not work, same for the file name! Use the under\_score for spaces if you need to.

The selected Top Level Source Type is **Schematic** because that's what we're planning on using first. This is not critical, as you can always add a new source file of any type later. The dialog box for the project wizard looks like:

| 🍃 New Project                                                      | Wizard                         | ×           |

|--------------------------------------------------------------------|--------------------------------|-------------|

| Create New Pro<br>Specify project location<br>Enter a name, locati |                                |             |

| Name:                                                              | Exampl_Project                 |             |

| Location:                                                          | C:\Xilinx\Exampl_Project       |             |

| Working Directory:<br>Description:                                 | C: \Xilinx \Exampl_Project     |             |

| Select the type of to                                              | p-level source for the project |             |

| Schematic                                                          |                                | <b>•</b>    |

| More Info                                                          |                                | Next Cancel |

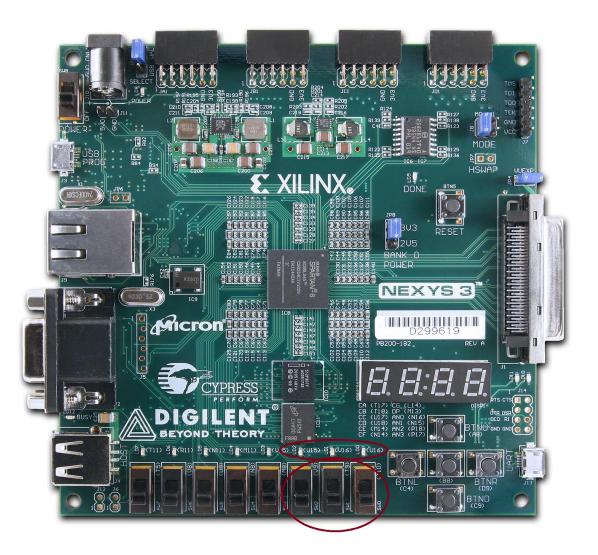

3. Click NEXT and in the next dialog box you should fill in the fields as shown here. You can do this in two ways, one is to select an "Evaluation Development Board" from the drop down list, and in our case you should select "Nexys 3". This will automatically fill out the board information in the next five sections. If the board does not exist in the list then you can set correct choices according to the following image.

We are using a **General Purpose** product in the **Xilinx Spartan6** family. The specific chip on the Nexys 3 board is an **XC6SLX16** in a **CSG324** package and the **-3** speed grade.

Attention: If you fail to set the correct options in this part, you will not be able to implement your design and program it on the Nexys 3 board!

Please make sure that the Synthesis Tool is **XST**, the Simulator is the **ISim**, and the Preferred Language is **Verilog**. This is very important for proper operation.

| Project Settings                                                                    |                     |   |

|-------------------------------------------------------------------------------------|---------------------|---|

|                                                                                     |                     |   |

| pecify device and project properties.<br>elect the device and design flow for the p | roject              |   |

| Property Name                                                                       | alue                |   |

| Evaluation Development Board                                                        | Nexys 3 Board       |   |

| Product Category                                                                    | All                 | + |

| Family                                                                              | Spartan6            | * |

| Device                                                                              | XC6SLX16            | * |

| Package                                                                             | CSG324              | * |

| Speed                                                                               | -3                  | 4 |

| Top-Level Source Type                                                               | Schemotic           | Ŧ |

| Synthesis Tool                                                                      | XST (VHDL/Verilog)  | - |

| Simulator                                                                           | ISim (VHDL/Verilog) | • |

| Preferred Language                                                                  | Verilog             | - |

| Property Specification in Project File                                              | Store all values    |   |

| Manual Compile Order                                                                |                     |   |

| VHDL Source Analysis Standard                                                       | VHDL-93             | - |

| Enable Message Filtering                                                            |                     |   |

4. Click NEXT and review the project summary page and then click FINISH, it is always good to double-check the summary to prevent headaches due to the problems you can face while implementing your design if the information is incorrect.

| 🌖 🍃 New Project Wiza                     | d                                                |               |

|------------------------------------------|--------------------------------------------------|---------------|

| Project Summary                          |                                                  |               |

| an a | a new project with the following specifications. |               |

| Project:                                 |                                                  |               |

| Project Name:                            | Example Project                                  |               |

| Project Path:                            | C:\Xilinx\Example Project                        |               |

| Working Direct                           | ory: C:\Xilinx\Example_Projec                    | t             |

| Description:                             |                                                  |               |

| Top Level Sour                           | ce Type: Schematic                               |               |

| Device:                                  |                                                  |               |

| Evaluation Dev                           | elopment Board: Nexys 3 Board                    |               |

| Device Family:                           | Spartan6                                         |               |

| Device:                                  | xc6slx16                                         |               |

| Package:                                 | csg324                                           |               |

| Speed:                                   | -3                                               |               |

| Top-Level Sour                           | ce Type: Schematic                               |               |

| Synthesis Tool                           | : XST (VHDL/Verilog)                             |               |

| Simulator: ISi                           | m (VHDL/Verilog)                                 |               |

| Preferred Lang                           | uage: Verilog                                    |               |

| Property Speci                           | fication in Project File: Sto                    | re all values |

| Manual Compile                           |                                                  |               |

| VHDL Source Ar                           | alysis Standard: VHDL-93                         |               |

| Message Filter                           | ing: disabled                                    |               |

| More Info                                |                                                  | Einish Cancel |

### Part II: Implement a function using Schematics

1. Now you should have a new project that targets the correct Xilinx part and other features of the ISE system. Notice the window to the left, and also notice the four tabs Start, Design, Files, ..., and in the case of an open schematic a Symbols tab will appear. Ensure that the "Implementation" choice is selected on the design pane.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0 ×      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| He Edt Yew Pipiest Source Decess Dools Window Layout Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| Dela Xiaa - Xaaaa - Xaaaa - Xaaaaa - Xaaaaa - Xaaaaa - Xaaaaaa - Xaaaaaaaa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2        |

| corp     Total       for any based on the state of the state |          |

| exite for the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| T No inside design produit is selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| C Desge Village                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ** 0 # × |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 📓 Cousta 🧿 Error 🚹 Tamonga 🙀 Feder Haskault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

2. Now you can create a new schematic in your project. Choose Project → New Source or right click on the Hierarchy section of the design windows to get the dialog box that adds a new source file to your project (or use the New Source widget on the left vertical tool bar). Source files can be of many types. Add a Schematic and name it simple\_logic for example. Make sure to both fill in the File Name and select the Schematic type from the list on the left. I've filled in my dialog box as shown below. Now click NEXT and after observing the summary page click FINISH.

|                                                                                              | New Source Wizard                                                                                                                                                                                                                                                     | ×                                                                        |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Select<br>P IP<br>So<br>So<br>So<br>So<br>So<br>So<br>So<br>So<br>So<br>So<br>So<br>So<br>So | tt Source Type<br>source type, file name and its location.<br>(CORE Generator & Architecture Wizard)<br>hematic<br>er Document<br>rilog Module<br>rilog Test Fixture<br>4DL Module<br>UDL Module<br>UDL Library<br>1DL Package<br>4DL Test Bench<br>nbedded Processor | File name:<br>simple_logic<br>Location:<br>C:\/ilinx\Example_Project<br> |

| More In                                                                                      | ıfo                                                                                                                                                                                                                                                                   | Next Cancel                                                              |

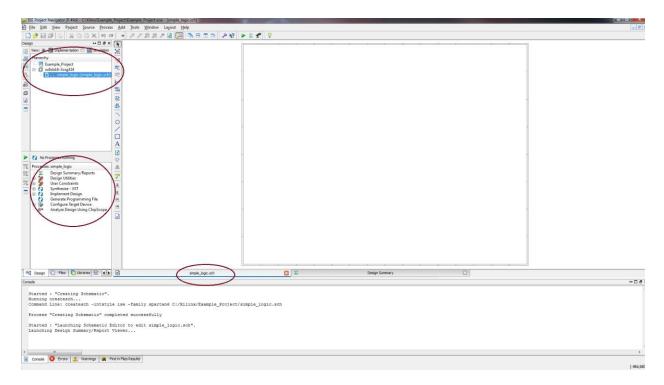

3. Now you have a blank schematic view, and also a Design Summary view in the main pane of the ISE window. You can switch between windows in the main pane with the tabs along the bottom. The (empty) schematic looks like below. Also note the Hierarchy created and the number of processes such as "Synthesis", "Implement", "Generate", etc. you can run on it.

4. If you don't see this exact view, you may be looking at a different tab in a window. Each pane has tabs at the bottom that let you switch to look at different things. For example, for the left pane in the image above there are multiple tabs to allow different things, "Files", "Snapshot", "Libraries", and "Symbols" tabs that you can click on and get different information about the project. The lower left pane is the Processes tab and Options tab that show different tools and steps. The main window in the figure above has a "simple\_logic.sch" tab for the new schematic, and a "Design Summary" tab. If you open more schematics, or other types of files (like Verilog files) the main pane will have additional tabs.

Now you can select components from the **Symbols** tab of the upper left pane and drag them to your schematic. You can narrow down your choices using the **Categories**, or by typing the first few characters of the symbol you're looking for in the **Symbol Name Filter**, or just scroll through the lists and see what's there. The important category for now is **Logic:** General logic gates. See the Lab handouts for restrictions on which logic gates you should use!

I'll grab some components from those Categories to make a very simple schematic to implement (A & (!B)) | (B & C) and drop them into the schematic page. Now we need to add wires and I/O markers by using the tools on the vertical bar between the schematic page and the side pane. Also pay attention to the "Options" tab at the bottom of the left pane. This section gives you some options on the schematic such as "selecting the entire wire branch" or "selecting line segments". This is good to know if you wanted to only remove a piece of wire and not everything that it is attached to.

| FISE Project Navigator (P.49d) - C:\Xilinx\Example_Pr                          | oject\Example_Project.xise - [simple_logic.sch*] |                         |                                       |                                        |                                         |

|--------------------------------------------------------------------------------|--------------------------------------------------|-------------------------|---------------------------------------|----------------------------------------|-----------------------------------------|

| Eile Edit View Project Source Process                                          | Add Tools Window Layout Help                     |                         |                                       |                                        | X                                       |

| □ ≥ □ ₽ ₽ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓                                    |                                                  | P 12 1 8                |                                       |                                        |                                         |

| Symbols ↔ □ @ ×                                                                | Ŋ                                                |                         |                                       |                                        | *                                       |

| Categories                                                                     | <u>د ا</u>                                       |                         |                                       |                                        |                                         |

| Decoder                                                                        |                                                  |                         |                                       |                                        |                                         |

| Flip_Flop                                                                      | ۳                                                |                         |                                       |                                        |                                         |

| General                                                                        |                                                  |                         |                                       |                                        |                                         |

| 10_FlipFlop                                                                    |                                                  |                         |                                       |                                        |                                         |

| ID_FlipFlop<br>ID_Intch<br>Vput/Output_Functions<br>LUT                        |                                                  |                         |                                       |                                        |                                         |

| LUT                                                                            | 2                                                |                         |                                       |                                        |                                         |

| - 10 Latch<br>- Aput/Output Functions<br>UUT<br>- Latch<br>- Logic<br>- Memory | 5                                                | · / / · · ·             | ■                                     |                                        |                                         |

|                                                                                |                                                  | INV .                   | · · · · · · · · · · · · · · · · · · · |                                        |                                         |

| chift Register                                                                 | 2                                                |                         |                                       |                                        |                                         |

| Shifter                                                                        |                                                  |                         | AND2                                  |                                        |                                         |

|                                                                                | $\vec{\mathbf{x}}$                               |                         |                                       |                                        |                                         |

| nor6                                                                           |                                                  |                         |                                       | ), ,),,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                         |

| - nor7                                                                         | 5 00 000000000000000000000000000000000           |                         |                                       | •                                      |                                         |

|                                                                                |                                                  |                         |                                       | UR2                                    |                                         |

| 012<br>016                                                                     | <b>p</b>                                         |                         |                                       |                                        |                                         |

| - or16<br>- or2                                                                |                                                  |                         |                                       |                                        |                                         |

| or7h1                                                                          |                                                  |                         | 8                                     |                                        |                                         |

| or2b2<br>or2l                                                                  |                                                  |                         | AND2                                  |                                        |                                         |

| or3b1                                                                          | <u>e</u> []                                      |                         |                                       |                                        | 101111111111111111111111111111111111111 |

| or3b2                                                                          |                                                  |                         |                                       |                                        |                                         |

| or3b3 +                                                                        |                                                  |                         |                                       |                                        |                                         |

| Symbol Name Filter                                                             |                                                  |                         |                                       |                                        |                                         |

|                                                                                |                                                  |                         |                                       |                                        |                                         |

| Orientation                                                                    |                                                  |                         |                                       |                                        |                                         |

| Rotate 0                                                                       |                                                  |                         |                                       |                                        |                                         |

| Symbol Info                                                                    | 4                                                | ·····                   |                                       | ·····                                  |                                         |

| s 🚺 Libraries 🏦 Symbols 🜮 Options 📢 🕨                                          | simple_logic.sch*                                | 2 2                     | Design Summary                        |                                        |                                         |

| Console                                                                        |                                                  |                         |                                       |                                        | +-□ 8 ×                                 |

|                                                                                |                                                  |                         |                                       |                                        |                                         |

| Started : "Creating Schematic".<br>Running createsch                           |                                                  |                         |                                       |                                        |                                         |

|                                                                                | ise -family spartan6 C:/Xilinx/Example_F         | roject/simple_logic.sch |                                       |                                        |                                         |

| Process "Creating Schematic" compl                                             | eted successfully                                |                         |                                       |                                        |                                         |

|                                                                                |                                                  |                         |                                       |                                        |                                         |

| Started : "Launching Schematic Edi<br>Launching Design Summary/Report Vi       | tor to edit simple_logic.sch".<br>ewer           |                         |                                       |                                        |                                         |

|                                                                                |                                                  |                         |                                       |                                        |                                         |

|                                                                                |                                                  |                         |                                       |                                        | -                                       |

| •                                                                              |                                                  |                         |                                       |                                        | ,                                       |

| 🗄 Console 🔕 Errors 🧘 Warnings 🐹 Find                                           | in Files Results                                 |                         |                                       |                                        |                                         |

|                                                                                |                                                  |                         |                                       |                                        | [636,1472]                              |

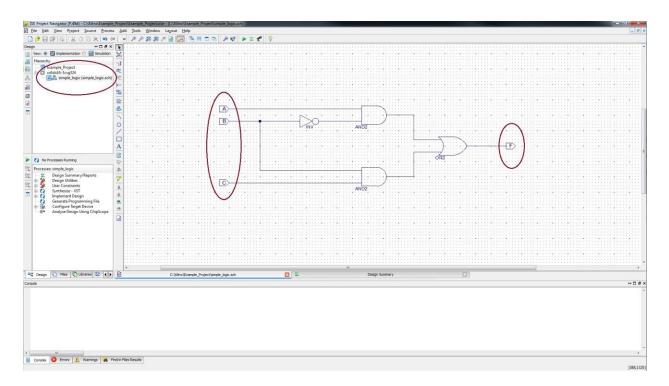

- 5. Use the wiring tool to wire up the components. It is in the tool bar and looks like a red line and a pencil. You could also use **Add** →**Wire** from the menu. I'm using the following components (from the **Logic** category) in this example:

- a. **and2:** a two-input AND gate

- b. or2: a two-input OR gate

- c. **inv:** an inverter

| 🥜 ISE Project Navigator (P.49d) - C:\Xilinx\Examp                                                                                                   |                       |                    |                       |                     |                                         |              |     |                                       |                                     |                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|-----------------------|---------------------|-----------------------------------------|--------------|-----|---------------------------------------|-------------------------------------|----------------------------------------|

| Eile Edit View Project Source Proc                                                                                                                  |                       |                    |                       |                     |                                         |              |     |                                       |                                     |                                        |

| 🗋 🏓 🛃 🦓 😓 🕺 🖉 🔲 🖌 🗠                                                                                                                                 | Cal »                 | / / Ø Ø / B        | 🖂 🗟 🗄 🗖 🖻             | ≯ k? ► Σ 📌          | <b>9</b>                                |              |     |                                       |                                     |                                        |

| Options ↔                                                                                                                                           | ×                     |                    |                       |                     |                                         |              |     |                                       |                                     |                                        |

| Select Options                                                                                                                                      |                       |                    |                       |                     |                                         |              |     |                                       | • • • • • • • • • • • • • • • • • • | · · · · · · · · · · · · · · · · · · ·  |

| When you click on a branch:                                                                                                                         | MC :                  |                    |                       |                     |                                         |              |     |                                       | ••••••                              |                                        |

| <ul> <li>Select the entire branch</li> <li>Select the line segment</li> </ul>                                                                       | 20                    |                    |                       |                     | • • • • • • • • • • • • • • • • • • • • |              |     |                                       | • • • • • • • • • • • • •           | ···· · · · · · · · · · · · · · · · · · |

| When you move an object:<br>Keep the connections to other<br>objects     Break the connections to other<br>objects                                  | √  <del>      =</del> |                    |                       |                     | 2                                       |              |     |                                       |                                     |                                        |

| When you use the area select tool, select                                                                                                           | 0                     |                    |                       | -                   |                                         | AND2         |     |                                       |                                     |                                        |

| <ul> <li>when you use the area select tool, select the objects that:</li> <li>Are endosed by the area</li> <li>Intersect the area</li> </ul>        |                       |                    |                       |                     |                                         |              |     | $\rightarrow$                         |                                     |                                        |

| When you use the area select tool, select:<br>Objects including attribute windows<br>Objects excluding attribute windows<br>Attributes windows only | ₽<br>₩<br>*           |                    | · · · · · · · · · · · |                     | · · · · · · · · · · · · · · · · · · ·   |              |     | OR2                                   | 5 · · · 5 · · · 5 · · · 5           |                                        |

|                                                                                                                                                     | <u>*</u>              |                    |                       |                     |                                         | AND2         |     | · · · · · · · · · · · · · · · · · · · |                                     |                                        |

|                                                                                                                                                     |                       |                    |                       |                     |                                         |              |     |                                       |                                     |                                        |

|                                                                                                                                                     |                       |                    |                       |                     | · · · · · · · · ·                       |              |     |                                       |                                     | · · · · · · · · · · · · · · · · · · ·  |

|                                                                                                                                                     | *                     |                    |                       |                     |                                         | m            |     |                                       |                                     |                                        |

| s 🚺 Libraries 🎡 Symbols 💱 Options 📢                                                                                                                 | ) <b>6</b>            |                    | simple_logic.sch*     |                     | 2                                       | Design Summa | ary |                                       |                                     |                                        |

| Console                                                                                                                                             |                       |                    |                       |                     |                                         |              |     |                                       |                                     |                                        |

| Started : "Creating Schematic"<br>Running createsch<br>Command Line: createsch -intst                                                               |                       | -family spartan6 ( | :/Xilinx/Example_     | Project/simple_logi | ic.sch                                  |              |     |                                       |                                     |                                        |

| Process "Creating Schematic" c                                                                                                                      |                       |                    |                       |                     |                                         |              |     |                                       |                                     |                                        |

| Started : "Launching Schematic<br>Launching Design Summary/Repor                                                                                    | Editor<br>t Viewe:    | to edit simple_log | pic.sch".             |                     |                                         |              |     |                                       |                                     |                                        |

| < m                                                                                                                                                 |                       |                    |                       |                     |                                         |              |     |                                       |                                     |                                        |

| 📱 Console 🔕 Errors 🔔 Warnings 🐹                                                                                                                     | Find in File          | s Results          |                       |                     |                                         |              |     |                                       |                                     |                                        |

6. Now place **I/O Markers** to the inputs and outputs. I've used the **I/O Marker** widget that looks like two little labels. You can also use the **Add**  $\rightarrow$  **I/O Marker** command from the menu. Click on the endpoints of the wire to add the marker.

| ISE Project Navigator (P.49d) - C:\Xilinx\Exam<br>Discussion                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                         | the second s |              |      |                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------|------|-----------------------------------------|

| Eile Edit View Project Source Pro                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                         |                                                                                                                |              |      | _ # ×                                   |

|                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                         | 5 P - X V                                                                                                      |              | <br> |                                         |

|                                                                                                                                                                                                                                     | ○         ▲           ○         ▲           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓           ○         ↓ | 2 8 8 7 8 2 2 3 5 7 7 2 4 1 7 2 4 1 7 1 7 1 7 1 7 1 7 1 7 1 7 1 7 1 7 1 |                                                                                                                | AND2         |      |                                         |

| Dutower 2 Sentes 2 Options of<br>Conset      Surried : "Creating Schemess:<br>Muning createsenh<br>Command Line: createsenhinse<br>Process "Creating Schematic"<br>Surried : "Launching Ghesault"     Launching Design Summary/Repo | *.<br>tyle ise -far<br>completed suc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | edit simple_logic.sch".                                                 | Ct/simple_logic.sch                                                                                            | Desgr Summer |      |                                         |

| Console O Errors 1 Warnings                                                                                                                                                                                                         | Find in Files Resul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | la -                                                                    |                                                                                                                |              | <br> | , , , , , , , , , , , , , , , , , , , , |

7. You should always change the name of the marker to whatever you want but choose a good identifier. You should double click the marker, or select the marker and right click to get a menu and choose **Edit**  $\rightarrow$  **Properties**. Then click on "Nets" and then edit the "Name", also observe the Port Polarity, then click OK. I'm calling the inputs **A**, **B** and **C** and the output **F**. An I/O Marker dialog box looks like:

| ategory<br>- I/O Markers | View and edit the | attributes of the selected r | nets    |             |

|--------------------------|-------------------|------------------------------|---------|-------------|

| LIXN_10                  | Name              | Value                        | Visible | New         |

|                          | Name              | A                            | Add     | Edit Traits |

|                          | PortPolarity      | Input 💌                      | Add     |             |

|                          |                   |                              |         |             |

|                          | 1                 |                              |         |             |

8. Now the resulting schematic looks like the following and it is ready for simulation or synthesis. Once your schematic is saved it should show up in the **Sources** pane in the upper left of the ISE screen.

When you are happy with your schematic (and your schematic will likely include other logic gates from the Logic category that I haven't used in this example!), save it. Hopefully you don't have any errors or warnings. If you do, you need to fix them.

# Part III: Implement a function using Verilog

This schematic representation of the function  $\mathbf{F} = (\mathbf{A} \ \& \ (!\mathbf{B})) | (\mathbf{B} \ \& \ \mathbf{C})$  is now ready for further processing either for simulation or implementation on the Nexys 3 board. Now we will explore the implementation of the same circuit using a "Verilog" module instead of a schematic, and both with have the same functionality.

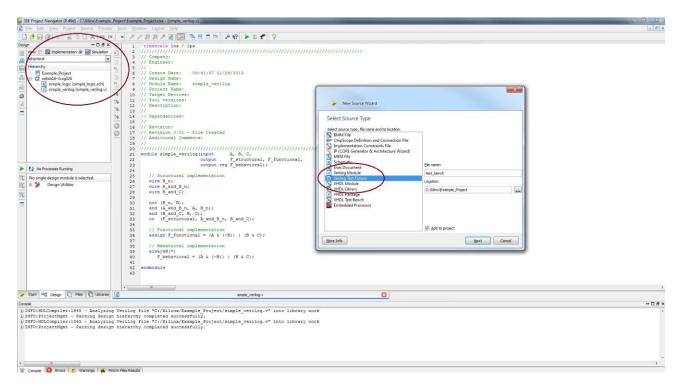

Just like step 2 of the schematic capture, we need to first add a new source. So again choose

**Project** → New Source or right click on the Hierarchy section of the design windows to get

the dialog box that adds a new source file to your project (or use the New Source widget on

the left vertical tool bar). This time choose "Verilog Module" and give it a file name.

Attention: it is important that you create the correct form of Verilog file for the specific use. Remember to ONLY use "Verilog Module" for *Implementation* and "Verilog Test Fixture" for *simulation* purposes. Do not do this the other way or things will not wok right

| Select Source Type                                                                                                                                                                                           |                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Select source type, file name and its location. BMM File ChipScope Definition and Connection File Implementation Constraints File IP (CORE Generator & Architecture Wizard) MEM File Schematic User Document | File name:                |

| Verilog Module                                                                                                                                                                                               | simple_verilog            |

| W Verilog Test Fixture                                                                                                                                                                                       | Location:                 |

| VHDL Library                                                                                                                                                                                                 | C:\Xilinx\Example_Project |

| P VHDL Package<br>W VHDL Test Bench<br>Embedded Processor                                                                                                                                                    |                           |

2. Click NEXT and you should see the module definition box. Here you can setup I/O names with correct polarity and a choice for buses and the width which we will be using in the future labs. Note that you do not have to add anything here right away and you can always add the I/O definitions to the module's header when it is created. After you're done click NEXT and then observe the summary page for a quick review of your I/O list.

| Define N     | lodule                          |          |    |         |     |     |  |

|--------------|---------------------------------|----------|----|---------|-----|-----|--|

|              | s for module.<br>simple_verilog |          |    |         |     |     |  |

|              | Port Name                       | Directio | on | Bus     | MSB | LSB |  |

| A            |                                 | input    | -  |         |     |     |  |

| В            |                                 | input    | -  |         |     |     |  |

| С            |                                 | input    |    |         |     |     |  |

| F_structural |                                 | output   | -  |         |     |     |  |

| F_functiona  |                                 | output   | -  |         |     |     |  |

| F_behaviora  | 1                               | output   | -  |         |     |     |  |

|              |                                 | input    |    |         |     |     |  |

|              |                                 | input    | -  | <u></u> |     |     |  |

|              |                                 | input    | -  |         |     |     |  |

|              |                                 | input    |    |         |     |     |  |

|              |                                 | input    | -  | (E)     |     |     |  |

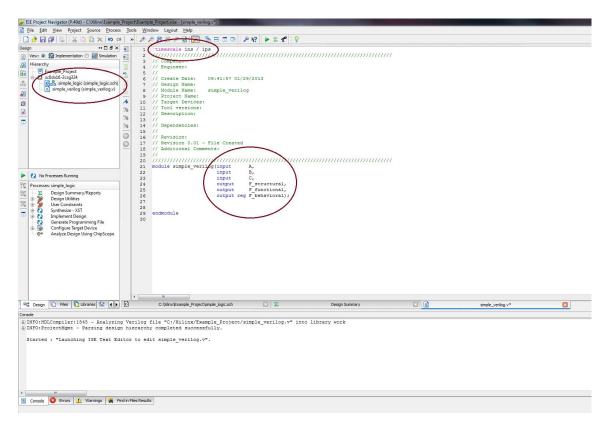

3. Now you should have a tab for the Verilog file opened in the ISE main pane. There is a line reading "**timescale 1ns / 1ps**". Please leave line alone and never delete it. It just lets the ISE know that each unit of time should be 1ns and have the resolution up to 1ps for any timing purposes (more on this later).

Next is the module header that contains the module name and the list of I/O as its parameters. If you notice I have declared multiple outputs to implement the same circuit using different HDL forms when writing in Verilog. These will all implement the same function  $\mathbf{F}$  represented by the schematic in Part I.

Also you should notice that the Verilog file is added to the Hierarchy next to the schematic as a part of this project. Now we're ready to implement the Verilog description of the function  $\mathbf{F}$  in the three intended forms.

4. For the implementation the three forms we have different formats. Sometimes we want to declare internal wires to connect things easily and in a more organized fashion, but if you didn't declare these wires, ISE will assume a single bit wire for the use.

**The Structural version:** This is done using gate primitives that are automatically taken from the Xilinx libraries (just as you would with a schematic) by calling their name and passing parameters, so for a two input gate we have the format "gate (output, input1, input2)" and this is just like doing a schematic in words.

**The Functional version:** Using the **"assign"** keyword to assign the results of the function expression to the output. The expression of the function looks a lot like how you would write it down on paper.

The Behavioral version: Using a synthesis directive called an "Always Block" we can implement the same function. The difference is that it only wakes up and assign the output

when any of the inputs are changes, hence the (\*) which means "any change". We will be using this format extensively in the future labs. One thing to notice is that any output being assigned inside of an always block needs to be declared as a "**reg**" for synthesis purposes, and that you cannot use the "assign" keyword inside of such block.

```

» 🏓 🔎 🛞 🏓 🗟 🦳 🔁 🗄 🖬 🖻 🥬 🌮 🛠 💡

1 `timescale 1ns / 1ps

3 // Company:

4 // Engineer:

5 //

6 // Create Date: 09:41:57 01/29/2013

7 // Design Name:

8 // Module Name: simple_verilog

9 // Project Name:

10

// Target Devices:

// Tool versions:

11

12 // Description:

13 //

14 // Dependencies:

15 //

16 // Revision:

// Revision 0.01 - File Created

17

// Additional Comments:

18

19 //

21module simple_verilog(inputA, B, C,22outputF_structural, F_functional,

23

output reg F behavioral);

24

// Structural implementation

25

wire B n;

26

wire A and B n;

27

28

wire B and C;

29

30

not (B n, B);

and (A and B n, A, B n);

31

and (B and C, B, C);

32

33

or (F structural, A and B n, B and C);

34

// Functional implementation

35

assign F functional = (A & (~B)) | (B & C);

36

37

38

// Behavioral implementation

always@(*)

39

F behavioral = (A \& (~B)) | (B \& C);

40

41

42 endmodule

43

III

X

simple verilog.v

```

5. You should always save your work multiple times as there always a slight chance that the tool may crash and you will lose your work. It is important to understand that hardware CAD tools are massive and complex so there is always a chance for unexpected or faulty behavior.

Now the circuit is ready for simulation or implementation on the board. It is important to notice that most processes are the same for both the schematic and the Verilog version of your design.

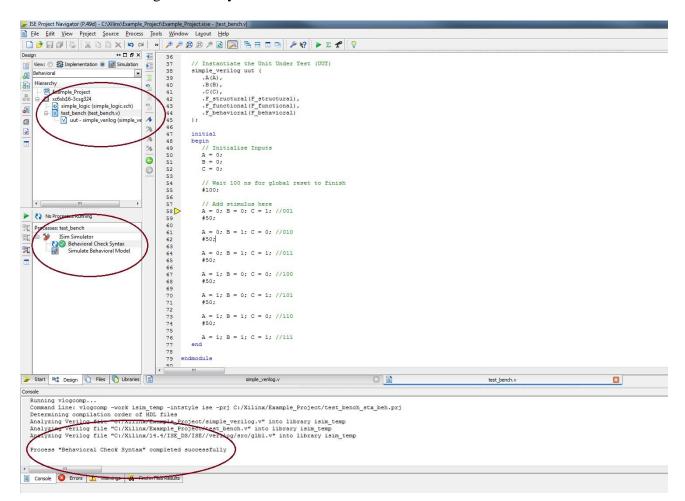

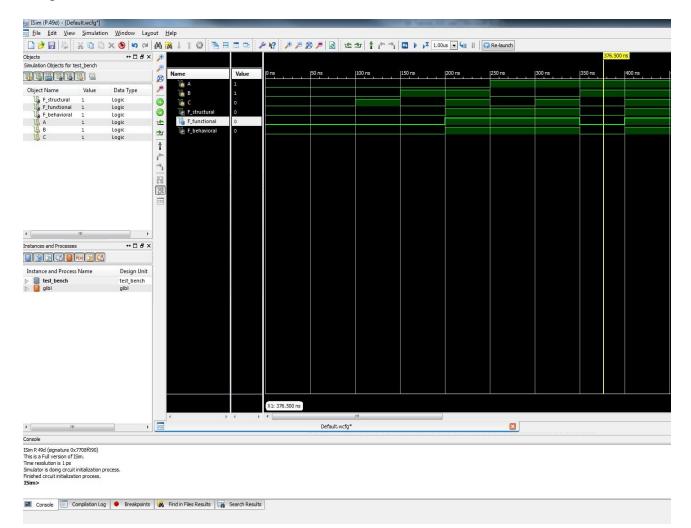

# Part IV: Simulate the schematic/Verilog circuit using the ISIM and a Verilog test fixture

Now that you have a saved schematic, you need to simulate its behavior. The simulator we'll use is the **ISE** built in simulator, which is essentially a Verilog simulator. The schematic that you just drew will be saved as a piece of Verilog behind your back if you choose to simulate it. In order to simulate the circuit you need:

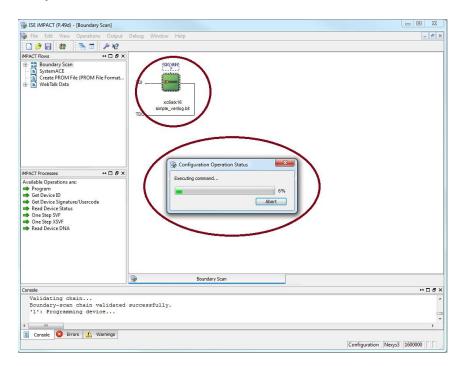

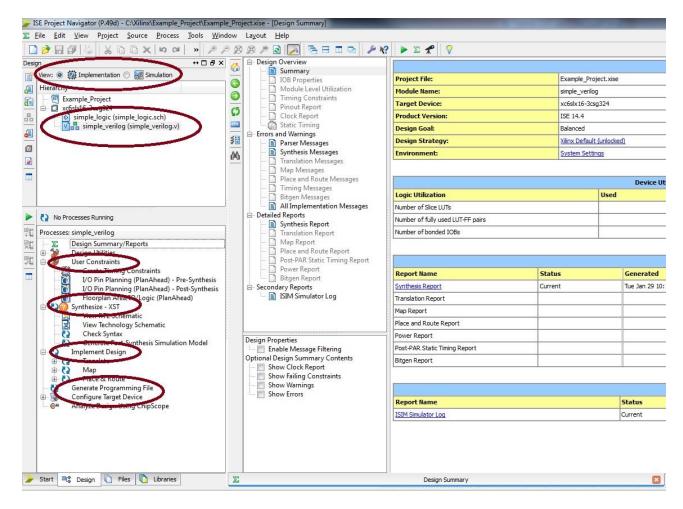

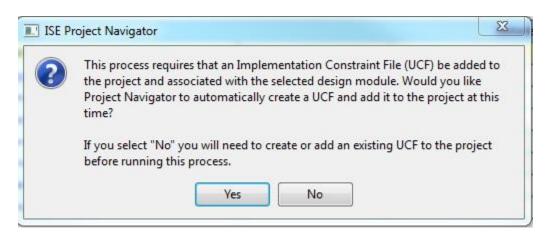

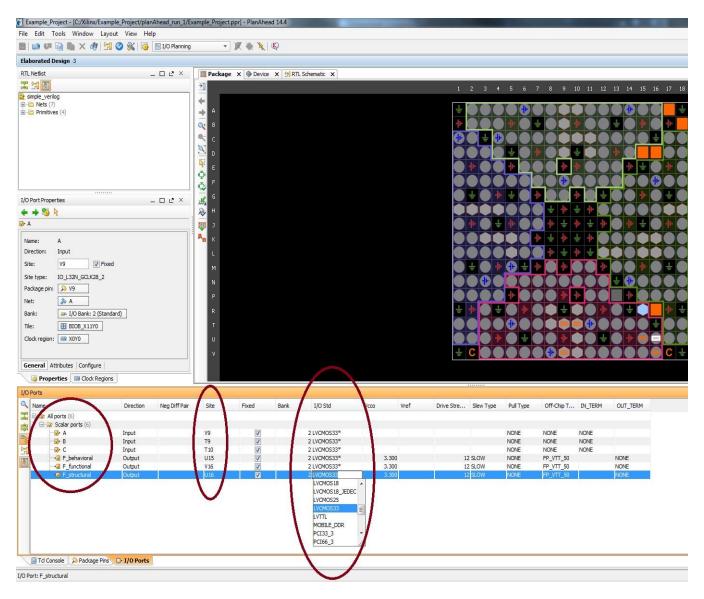

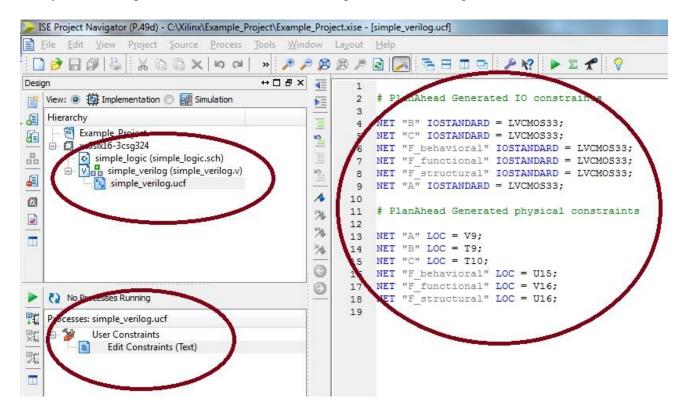

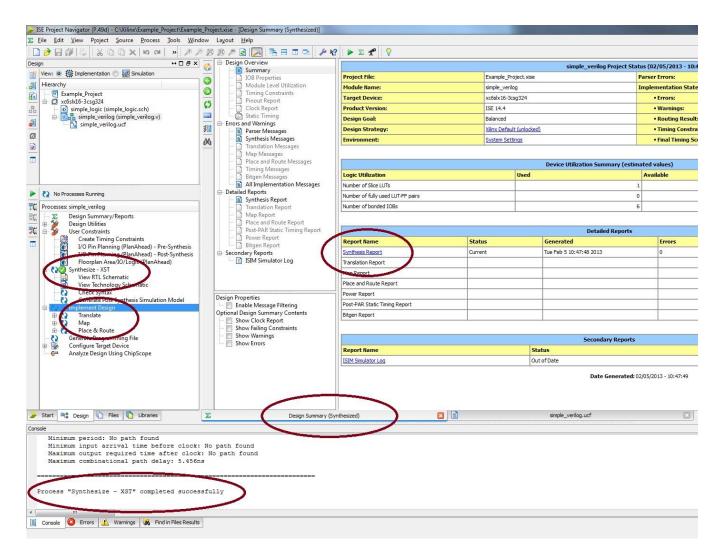

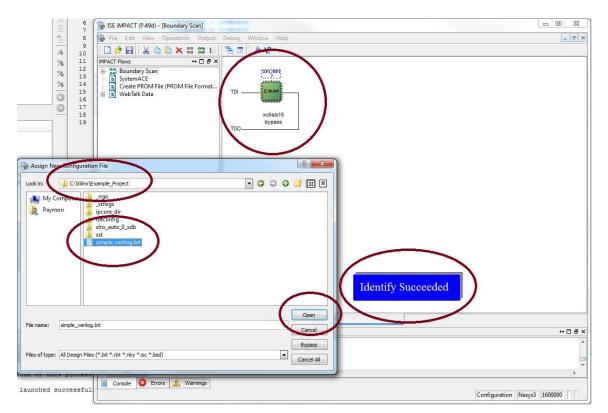

**Testbench:** is a file that becomes a top module to your design and applies inputs to your circuit, and potentially checks that the outputs are correct. This will be another Verilog file written slightly differently than circuit implementation. The testbench will instantiate one copy of your circuit, and call it **UUT** for "Unit Under Test". You will then write the Verilog statements that set the inputs to your circuit (the UUT), and looks at the outputs produced by your circuit. You need to know only very basic Verilog syntax to do this.