## What Happens

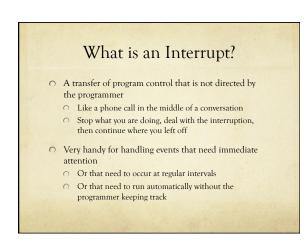

• An interrupt is signaled somehow

- A phone rings

- The AVR stops running user code and checks to see what caused the interrupt

- $\, \cap \,$  Stop your conversation and check which phone is ringing

- The AVR runs an Interrupt Service Routing (ISR) related to that interrupt

- Answer the phone and handle the call

- The AVR restores the system state and picks up the user code where it left off

- Hang up and resume your previous conversation

# On Arduino/AVR, there are three types External: A signal outside the chip (connected to a pin) Timer: Internal to the chip, like an alarm clock Device: One of the AVR devices (USART, SPI, ADC, EEPROM) signals that it needs attention

### Example: USART

- USART handles the serial communication between Arduino and the host

- Why not just check for a new character in a loop?

- How frequently would you have to check?

- How much processor time would be spend checking?

# Example: USART

• Serial port at 9600 baud (9600 bits/sec)

- Each bit is sent at 9.6 kHz (close to 10kHz)

- Each bit takes around 100usec

- Around 10 bits required for each character

- So, one character every 1msec or so

- If the USART is buffered, you have about 1msec to get a character before it's overwritten by the next one

So, you have to check faster than once every millisecond to keep up (around 1000 times a sec)

If your main loop is not doing anything else, you can do this, but if you're doing other things, or communicating at faster speeds, it gets ugly fast

### Example: USART

- Instead set up an interrupt handler for the USART

- The USART will cause an interrupt each time it receives a complete character

- The Interrupt Service Routine (ISR) for this USARTreceive event will be called

- The ISR will take the character from the USART and put it in a buffer for your program to use

- You never have to check the USART directly, characters just show up in your program's buffer as they arrive

# Types of Interrupts

○ On Arduino/AVR, there are three types

- External: A signal outside the chip (connected to a pin)

- Timer: Internal to the chip, like an alarm clock

- Device: One of the AVR devices (USART, SPI, ADC, EEPROM) signals that it needs attention

### External Interrupts

○ An external event (signal on an input pin) causes an interrupt

- A button, a sensor, an external chip, etc.

- There are two external interrupt pins on Arduino

O Interrupt 0 (Pin 2) and Interrupt 1 (Pin 3)

- Supported by the Arduino software

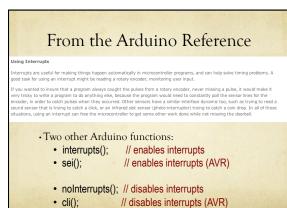

### attachInterrupt(interrupt#, func-name, mode);

- Interrupt# is 0 or 1

- Func-name is the name of the ISR function

- Mode is LOW, CHANGE, RISING, or FALLING

# AttachInterrupt(interrupt, function, mode) Description Specifies a function to call when an external interrupt occurs. Replaces any previous function that was attached to the interrupt. Most Anguine boards have two external interrupts: numbers 0 (on digital pin 2) and 1 (on digital pin 3). The Anguine Mega has an additional four: numbers 2 (pin 21), 3 (pin 20), 4 (pin 19), and 5 (pin 18). Parameters interrupt: the number of the interrupt (mt) function: the function to call when the interrupt occurs; this function must take no parameters and return nothing. This function is sometimes referred to as an interrupt active. editions: the function to call when the interrupt accurs; this function must take no parameters and return nothing. This function is sometimes referred to as an interrupt active. e. Out to tagget the interrupt active. e. Out to tagget the interrupt advice returned. e. Using to the interrupt advice route. e. Out to tagget the interrupt advice route. e. Out to tagget the interrupt advice route. e. Out to tagget the interrupt advice route. e. Using to to target the interrupt advice route. e. Harting to tagget the interrupt advice route. e. Harting to target the interrupt advice route to high. e. Harting to target the interrupt advice route to high. e. Harting to target the interrupt advice route target the target target target target target. e. Harting to target the interrupt to high.</td

ence Language (extended) | Libraries | Comparison | Change

External Interrupt Example int pin = 13; // the builtin LED pin volatile int state = LOW; // Hold the state of the LED // Note that external interrupt 0 looks for changes on // digital pin 2 of the Arduino board void setup0 { pinMode(pin, OUTPUT); attachInterrupt(0, blink, CHANGE); // attach ISR interrupts(); // enable interrupts (actually not needed) } void loop0 { digitalWrite(pin, state); // Main code writes to LED } void blink() { state = !state; } // ISR changes LED state

# Aside: Volatile Qualifier

### volatile keyword

volatile is a keyword known as a variable qualiñer, it is usually used before the datatype of a variable, to modify the way in which he compiler and subsequent program treats the variable.

Declaring a variable volatile is a directive to the compiler. The compiler is software which translates your C/C++ code into the machine code, which are the real instructions for the Atmega chip in the Arduino.

Specifically, it directs the compiler to load the variable from RAM and not from a storage register, which is a temporary memory location where program variables are stored and manipulated. Under certain conditions, the value for a variable stored in register can be inaccurate.

A variable should be declared volatile whenever its value can be changed by something beyond the control of the code section in which it appears, such as a concurrently executing thread. In the Arduino, the only place that this is likely to occur is in sections of code associated with interrupts, called an interrupt service routine.

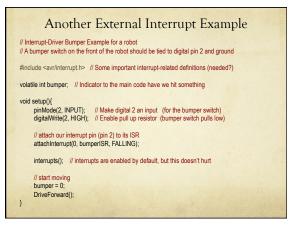

### Another External Interrupt Example

### // The interrupt hardware calls this when we hit our bumper void bumperISR(){

Stop();

// stop forward motion

bumper = 1;

// indicate that the bumper was hit

DriveBackward();

// stop to roverse

delay(1000);

// back up for 1 second

TumRight();

// trun right (away from obstacle)

DriveForward();

// drive off again...

### void loop(){

// You can put any other robot driving commands here // but you don't need to check for the bumper here. // It's handled by the external interrupt

// If you want to, you can check the value of the bumper // variable in the main code to see if it was hit. If you do // check, you can reset it to 0 so that you can continue to // check later.

### External Interrupt Summary

- AVR ATMega328p has 2 external interrupts

0 (on Arduino pin 2) and 1 (on Arduino pin 3)

- Use attachInterrupt (int#, ISR-name, mode); to attach an ISR to an external interrupt

- Make sure to provide a function definition for ISR-name

- Choose mode as LOW, CHANGE, RISING, FALLING

- If the main code looks at a variable that is set in the ISR, make sure that variable is **volatile**

- detachInterrupt(int#); is also available

- o interrupts(); and noInterrupts(); turn them on and off

# Aside – more external interrupts

- Arduino (AVR) has only 2 external interrupt pins

- Actually, if you want CHANGE mode, there are lots more pins you can use (pretty much all the Arduino pins)

- But, that requires a little deep dark secret AVR-hacking

- So, unless you need it, don't worry about it

- If you do need it Look at the PC Int code on the Arduino site

- Magic code that allows triggering an interrupt from any pin on the Arduino...

- I'll put a link on the class web site

# On Arduino/AVR, there are three types External: A signal outside the chip (connected to a pin) Timer: Internal to the chip, like an alarm clock Device: One of the AVR devices (USART, SPI, ADC, EEPROM) signals that it needs attention

# Motivation • Arduino 101 – blinky LED Problem - Arduino is just wasting time during the delay. It can't be used for anything else. int ledPin = 13: // LED connected to digital pin 13 void setup() pinMode(ledPin, OUTPUT); // initialize the digital pin as an output: void loop() { digitalWrite(ledPin, HIGH); // set the LED on delay(1000); // wait for a second digitalWrite(ledPin, LOW); // set the LED off delay(1000); // wait for a second

### Motivation

### ○ Arduino 101 – blinky LED

- Non-delay version use a timer to see if it's time to blink

- Can use the Arduino for other things in the meantime

- But, the programmer has to manage this activity

- Don't use delay that ties up the processor while it's delaying

- Instead, there is a millis(); function that returns the current number of milliseconds since the last system reset O Based on internal timers!

- Use that to check occasionally if enough time has passed that you should flip the LED again

- You can do other things between checking

### non-delay blinky

const int ledPin = 13; // LED connected to digital pin 13 int LedState = 0; // Remember state of LED long previousMillis = 0; // Store last time LED flashed long interval = 1000; // Interval at which to blink

void setup() {

pinMode(ledPin, OUTPUT); }

- if ucdstate == LOW) ledstate = HIOT; ess ledstate = LOW; digralWitte(ledPin, ledState); // set the LED with the ledState of the variable: // Outside of this check, we can do other things... // Depending on how long the other things take, we might delay slightly longer than // 1000 millisee, but that's probably fine for this application

- 1

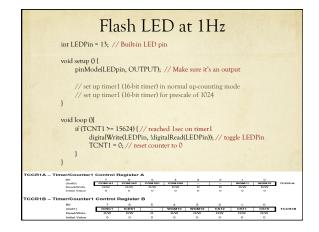

# Motivation

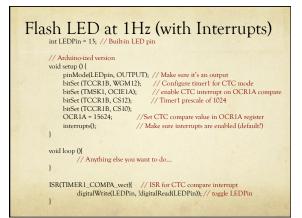

- Instead, we could use interrupts

- Interrupt the processor every 1sec (for example)

- Change the state of the LED

- Then continue with program execution

- Keeps the LED blinking at a fixed rate

- Doesn't require any attention in the main program

• This is a general technique, not just for LED-blinking!

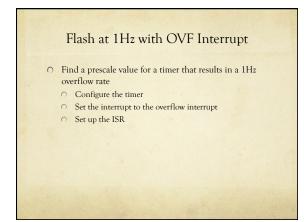

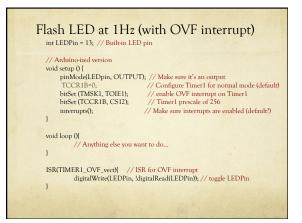

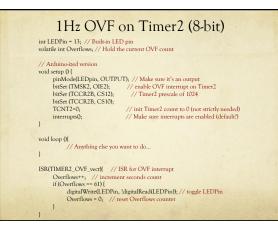

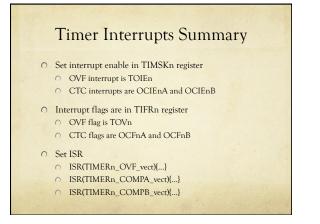

### Agenda

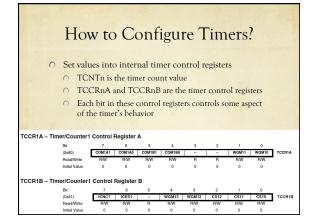

- First look at timers

- What are they?

- How to read/write timer values?

- How to configure them?

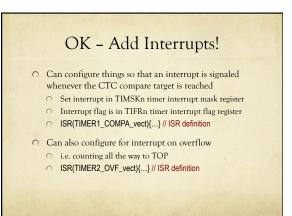

- Then look at how a timer can cause an interrupt

- Like an alarm clock

- When a timer alarm goes off, and ISR may be called

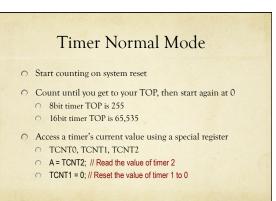

# **AVR** Timers

### ○ Timers are like on-chip alarm clocks

- They count (tick) once for each system clock tick O 16MHz for Arduino

- Your program can check, and reset the count value

- You can also "prescale" the timer's clock so that it's

- counting more slowly than the 16MHz Arduino clock • You can also have the timer set an alarm when the

- count gets to some particular value ○ The alarm is an interrupt

- You can define the ISR for that timer alarm

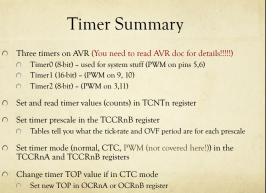

### **AVR** Timers

- Our Arduino's AVR has three internal timers

- Timer0: an 8-bit timer (counts 0 to 255)

O Used for system timing, millis0; micros0;, etc.

- o and PWM on pins 5 and 6

o Timer1: a 16-bit timer (counts 0 to 65,535)

- Used for PWM on pins 9 and 10

- Timer 2: an 8-bit timer (counts 0 to 255)

Used for PWM on pins 3 and 11

- Don't use Timer0 it will mess things up...

- If you use Timer1 or Timer2, you will lose PWM on some pins...

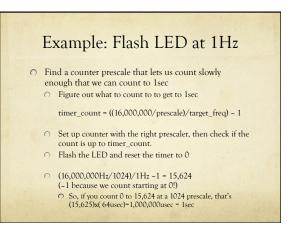

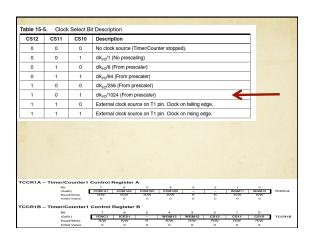

### How Fast to Count?

- 16MHz is fast!

- 16,000,000 ticks/sec, 62.5ns per clock tick

- A "prescaler" slows down the rate at which a timer counts by some factor

- Increases the range of time you can count, but makes the smallest tick resolution larger

- O Timer0 and Timer1: divide clock by 1, 8, 64, 256, 1024

- O Timer2: divide clock by 1, 8, 32, 64, 128, 256, 1024

### Resolution/Timing with Prescaler

| Prescale Value | Tick Time | OVF<br>frequency | OVF Period |

|----------------|-----------|------------------|------------|

| 1              | 62.5nsec  | 62.5 kHz         | 16usec     |

| 8              | 500nsec   | 7.8125kHZ        | 128usec    |

| 32             | 2usec     | 1.953125kHZ      | 512usec    |

| 64             | 4usec     | 976.5625Hz       | 1.024msec  |

| 128            | 8usec     | ~496.03Hz        | 2.048msec  |

| 256            | 16usec    | ~244.14Hz        | 4.096msec  |

| 1024           | 64usec    | ~61.04Hz         | 16.384msec |

8-bit counter at 16MHz system clock frequency (Timer2) OVF = Overflow (time it takes to count from 0 to TOP) TOP = 255 for an 8-bit counter

| Prescale Valu | e Tick Time | OVF<br>frequency | OVF Period  |

|---------------|-------------|------------------|-------------|

| 1             | 62.5nsec    | ~244.14Hz        | 4.096msec   |

| 8             | 500nsec     | ~30.52HZ         | 32.768msec  |

| 64            | 4usec       | ~3.815Hz         | 262.144msec |

| 256           | 16usec      | ~0.954Hz         | ~ 1.05sec   |

| 1024          | 64usec      | ~0.238Hz         | ~4.19sec    |

16-bit counter at 16MHz system clock frequency (Timer1) OVF = Overflow (time it takes to count from 0 to TOP) TOP = 16,535 for a 16-bit counter

| Table   | 15-1.    | Compare         | Output N         | lode, nor        | I-PWM                  |                |         |          |                       |                     |      | 1. Salaria |

|---------|----------|-----------------|------------------|------------------|------------------------|----------------|---------|----------|-----------------------|---------------------|------|------------|

| COI     | M1A1/CO  | W1B1            | COM1A0           | COM1B0           | Desc                   | ription        |         |          |                       |                     |      |            |

|         | 0        |                 | (                | D                | Norm                   | al port op     | eration | , OC1A/C | C1B disco             | nnected.            |      | _          |

|         | 0        |                 |                  | 1                | Toggl                  | e OC1A/C       | DC1B o  | n Compa  | re Match.             |                     |      |            |

|         | 1        |                 |                  | D                | Clear<br>low le        |                | C1B or  | Compare  | Match (Se             | et output to        |      |            |

|         | 1        |                 |                  | 1                | high                   |                | B on C  | ompare l | Match (Set            | output to           |      |            |

| Table 1 | 5-4. Wav | eform Gen       | eration Mode     | Bit Descrip      | tion <sup>(1)</sup>    |                |         |          |                       |                     |      |            |

| Mode    | WGM13    | WGM12<br>(CTC1) | WGM11<br>(PWM11) | WGM10<br>(PWM10) | Timer/Cor<br>Operation | unter Mode     | of      | TOP      | Update of<br>OCR1x at | TOV1 Flag<br>Set on |      |            |

| 0       | 0        | 0               | 0                | 0                | Normal                 |                |         | 0xFFFF   | Immediate             | MAX                 |      | _          |

| 1       | 0        | 0               | 0                | 1                | PWM, Pha               | ise Correct, I | 8-bit   | 0x00FF   | TOP                   | BOTTOM              |      |            |

| 2       | 0        | 0               | 1                | 0                | PWM, Pha               | ise Correct, I | 9-bit   | 0x01FF   | TOP                   | BOTTOM              |      |            |

| 3       | 0        | 0               | 1                | 1                | PWM, Pha               | se Correct,    | 10-bit  | 0x03FF   | TOP                   | BOTTOM              |      |            |

| 4       | 0        | 1               | 0                | 0                | CTC                    |                |         | OCR1A    | Immediate             | MAX                 |      |            |

| 5       | 0        | 1               | 0                | 1                | Fast PWM               | . 8-bit        |         | 0x00FF   | BOTTOM                | TOP                 |      |            |

| 6       | 0        | 1               | 1                | 0                | Fast PWM               | . 9-bit        |         | 0x01FF   | BOTTOM                | TOP                 |      |            |

| 7       | 0        | 1               | 1                | 1                | Fast PWM               | , 10-bit       |         | 0x03FF   | BOTTOM                | TOP                 |      |            |

| 8       | 1        | 0               | 0                | 0                | PWM, Pha<br>Correct    | ise and Freq   | uency   | ICR1     | BOTTOM                | BOTTOM              |      |            |

| 9       | 1        | 0               | 0                | 1                | PWM, Pha<br>Correct    | ise and Freq   | uency   | OCR1A    | BOTTOM                | BOTTOM              |      |            |

| TCCF    | RIA – TI |                 | unter1 Co        |                  |                        |                |         |          |                       |                     |      |            |

|         |          | Bit<br>(0x80)   |                  | 7                | 6<br>20M1A0            | 5<br>COM181    | 4 COM   | 80       | 3 2                   | WGMI                | 0    | TCCRIA     |

|         |          | ReadA           | Vrite            | R/W              | R/W                    | RAW            | RA      | v .      | R F                   | R/W                 | R/W  |            |

|         |          | Initial N       | fabue            | 0                | 0                      | 0              | 0       |          | 0 0                   | • •                 | 0    |            |

| TCCF    | R18 - Ti | mer/Co          | unter1 Co        | ontrol Re        | egister i              | в              |         |          |                       |                     |      |            |

|         |          | Bit             | _                | 7                | 6                      | 6              | 4       |          |                       |                     | 0    |            |

|         |          | (0x81)          |                  | ICNC1            | ICES1                  | -              | WGM     |          |                       |                     | CS10 | TCCRIB     |

|         |          | Read/           |                  | R/W              | R/W                    | R              | RM      |          | W RA                  |                     | R/W  |            |

|         |          | Initial V       | raute            | 0                | 0                      | 0              | 0       |          | ) 0                   | 0                   | 0    |            |

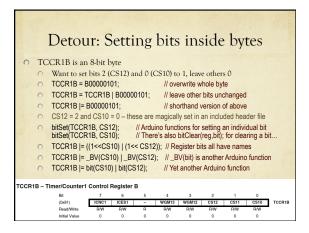

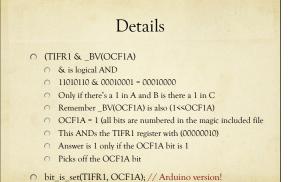

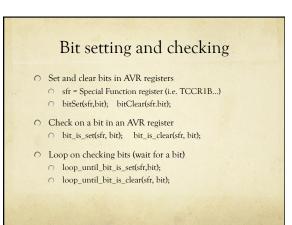

### Detour: Setting Bits

$\cap$  | = logical OR

- 0 00101101 | 01100011 = 01101111

- If there's a 1 in A or B, there's a 1 in C

### ○ (1<<CS12)

- CS12 is defined to be 2 (in a secret included file)

- $\circ$  (1<<2) is 1 shifted two places to the left in the byte

- this is 00000100

- CS10 = 0

So ((1<<CS12) | (1<<CS10)) = 00000100 | 00000001</li>

- This equals 00000101

- \_BV(CS12) = bit(CS12) = (1<<CS12) = 00000100

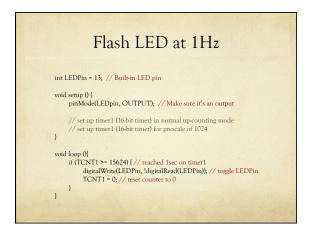

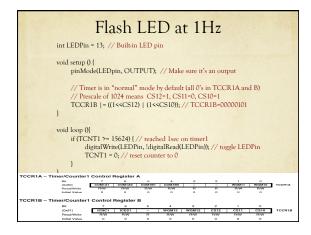

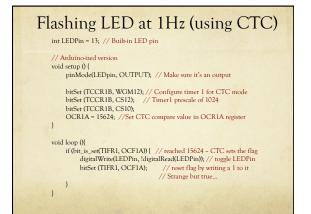

|          | int LEDPir           |                      |            |             | D a        | .t 11       | Hz            |           |       |        |

|----------|----------------------|----------------------|------------|-------------|------------|-------------|---------------|-----------|-------|--------|

|          | void setup           | ){                   |            |             |            |             |               |           |       |        |

|          | pinMo                | ode(LED <sub>I</sub> | oin, OU1   | FPUT)       | // Mak     | e sure it   | 's an ou      | tput      |       |        |

|          | // Tir               | ner is in "          | 'normal"   | mode        | by defaul  | lt (all O's | in TCC        | R1A an    | id B) |        |

|          | // Pre               | scale of 1           | 024 mea    | ns CS       | 12=1, CS   | 11=0, C     | S10=1         |           |       |        |

|          | bitSet               | TCCR1H               | 3. CS12);  |             | // TCCF    | 1B=000      | 00100         |           |       |        |

|          |                      | TCCR1                |            |             |            |             |               |           |       |        |

|          | 1                    |                      | , 0010),   |             | ,          |             | 00101         |           |       |        |

|          | 1                    |                      |            |             |            |             |               |           |       |        |

|          | void loop ()         | {                    |            |             |            |             |               |           |       |        |

|          | if (TC               | NT1 >= 1             | 5624) {    | // reac     | hed 1sec   | on time     | 1             |           |       |        |

|          |                      | igitalWri            |            |             |            |             |               | aalo I FI | Pin   |        |

|          |                      | CNT1 =               |            |             |            | LEDIM       | <i>,,,,</i> w | ggit LLI  | 51 m  |        |

|          | }                    | CIVIT-               | 0,77 ies   | et cour     | iter to o  |             |               |           |       |        |

| TCCR1A - | . Timer/Counter      | Control I            | Register   | A           |            |             |               |           |       |        |

|          | 84                   | 7                    |            | 5<br>COM181 | 4          | з           | 2             | WGM11     | 0     |        |

|          | (0x80)<br>Read/Write | R/W                  | R/W        | RAW         | R/W        | R           | R             | R/W       | R/W   | TCCHIA |

|          | Initial Value        | 0                    | 0          | 0           | 0          | 0           | 0             | 0         | 0     |        |

| CCR1B -  | - Timer/Counter      | Control              | Register   |             |            |             |               |           |       |        |

|          | Bit<br>(Ox81)        | 7<br>ICNC1           | 6<br>ICES1 | 6           | 4<br>WGM13 | 3<br>WGM12  | 2             | 1         | 0     | тесятв |

|          | (0x81)<br>Read/Write | B/W                  | R/W        | 8           | RW         | R/W         | RW            | RAW       | R/W   | 100mb  |

|          | Initial Value        | 0                    | 0          | 0           | 0          | 0           | 0             | 0         | 0     |        |

# Flash LEDD at 1/minute int LEDPin = 13; // Built-in LED pin int ElapsedSeconds = 0; // Keep track of seconds void setup 0 { pinMode(LEDpin, OUTPUT); // Make sure it's an output // Timer is in "normal" mode by default (all 0's in TCCR1A and B) // Prescale of 1024 means CS12=1, CS11=0, CS10=1 TCCR1B = ((1<<CS12) | (1<<CS10); // TCCR1B=00000101 } void loop 0{ if (TCNT1 = 15624) {// reached lsec on timer1 TCNT1 = 0; // reset timer1 count to 0 ElapsedSeconds == 60) { // Check for Tmin ElapsedSeconds == 60) { // Check for Tmin ElapsedSeconds = 0; // reset seconds counter digitalWrite(LEDPin, !digitalRead(LEDPin); // toggle LEDPin ) }</pre>

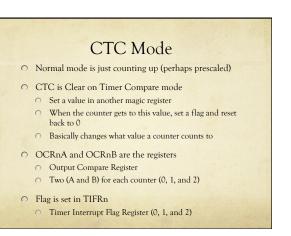

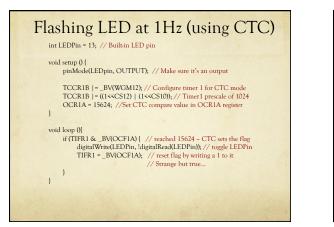

|        |           |                  | S                | lett             | ing CT(                             | CN     | Лod                   | e                   |             |        |

|--------|-----------|------------------|------------------|------------------|-------------------------------------|--------|-----------------------|---------------------|-------------|--------|

| able 1 | 5-4. Wave | oform Gene       | ration Mode      | Bit Descrip      | tion <sup>(1)</sup>                 |        |                       |                     |             |        |

| Mode   | WGM13     | WGM12<br>(CTC1)  | WGM11<br>(PWM11) | WGM10<br>(PWM10) | Timer/Counter Mode of<br>Operation  | TOP    | Update of<br>OCR1x at | TOV1 Flag<br>Set on |             |        |

| 0      | 0         | 0                | 0                | 0                | Normal                              | 0xFFFF | Immediate             | MAX                 |             |        |

| 1      | 0         | 0                | 0                | 1                | PWM, Phase Correct, 8-bit           | 0x00FF | TOP                   | BOTTOM              |             |        |

| 2      | 0         | 0                | 1                | 0                | PWM, Phase Correct, 9-bit           | 0x01FF | TOP                   | BOTTOM              |             |        |

| 3      | 0         | 0                | 1                | 1                | PWM, Phase Correct, 10-bit          | 0x03FF | TOP                   | BOTTOM              |             |        |

| 4      | 0         | 1                | 0                | 0                | CTC                                 | OCR1A  | Immediate             | MAX                 | <u> </u>    |        |

| 5      | 0         | 1                | 0                | 1                | Fast PWM, 8-bit                     | 0x00FF | BOTTOM                | TOP                 | •           |        |

| 6      | 0         | 1                | 1                | 0                | Fast PWM, 9-bit                     | 0x01FF | BOTTOM                | TOP                 |             |        |

| 7      | 0         | 1                | 1                | 1                | Fast PWM, 10-bit                    | 0x03FF | BOTTOM                | TOP                 |             |        |

| 8      | 1         | 0                | 0                | 0                | PWM, Phase and Frequency<br>Correct | ICR1   | BOTTOM                | BOTTOM              |             |        |

| 9      | 1         | 0                | 0                | 1                | PWM, Phase and Frequency<br>Correct | OCR1A  | BOTTOM                | BOTTOM              |             |        |

| CCF    | RIA - TI  |                  | inter1 Co        |                  | igister A                           |        |                       |                     |             |        |

|        |           | Dit<br>(Ox80)    |                  |                  |                                     | 4180   | 0 2                   |                     |             | TOOR1. |

|        |           | Initial V        |                  | 0                |                                     | w      | 0 0                   |                     | 0           |        |

| CCF    | R1B – Ti  |                  | inter1 Co        |                  | egister B                           |        |                       |                     |             |        |

|        |           | ENt              |                  | 7                | 6 5 4                               |        | 2 2                   | 1                   | 0           | TCCR   |

|        |           | (0x81)<br>Read/M |                  | R/W              | R/W R R/                            | w B    | M12 C91               |                     | CS10<br>R/W | т      |

|        |           | Initial V        | alue             | 0                | 0 0 0                               |        | o 0                   | 0                   | 0           |        |

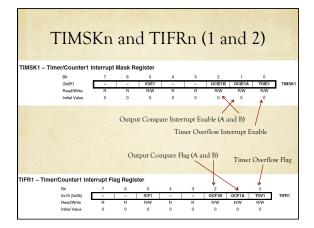

| Flag is se      | t in th                               | e TIF                                                             | 'Rn reg                                                                    | ister                                                                                     |                                                           |                                                                                            |                                                                                                                                                                                                                                          |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|---------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r/Counter1 Inte | errupt Fla                            | ag Regi                                                           | ster                                                                       |                                                                                           |                                                           |                                                                                            |                                                                                                                                                                                                                                          |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Bit             | 7                                     | 6                                                                 | 5                                                                          | 4                                                                                         | 3                                                         | 2                                                                                          | 1                                                                                                                                                                                                                                        | 0                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x16 (0x36)     | -                                     | -                                                                 | ICF1                                                                       | -                                                                                         | -                                                         | OCF1B                                                                                      | OCF1A                                                                                                                                                                                                                                    | TOV1                                                   | TIFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Read/Write      | R                                     |                                                                   |                                                                            |                                                                                           |                                                           |                                                                                            |                                                                                                                                                                                                                                          | R/W                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Initial Value   | 0                                     | 0                                                                 | 0                                                                          | 0                                                                                         | 0                                                         | 0                                                                                          | 0                                                                                                                                                                                                                                        | 0                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |                                       |                                                                   |                                                                            |                                                                                           |                                                           |                                                                                            |                                                                                                                                                                                                                                          |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |                                       |                                                                   |                                                                            |                                                                                           |                                                           |                                                                                            |                                                                                                                                                                                                                                          |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |                                       |                                                                   |                                                                            |                                                                                           |                                                           |                                                                                            |                                                                                                                                                                                                                                          |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |                                       |                                                                   |                                                                            |                                                                                           |                                                           |                                                                                            |                                                                                                                                                                                                                                          |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |                                       |                                                                   |                                                                            |                                                                                           |                                                           |                                                                                            |                                                                                                                                                                                                                                          |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | r/Counter1 Inte<br>Bit<br>0x16 (0x36) | r/Counter1 Interrupt Fia<br>Bit 7<br>0x16 (0x36) -<br>ReadWrite R | r/Counter1 Interrupt Flag Regis<br>Bit 7 6<br>0x16 (0x36)<br>ReadWrite R R | //Counter1 Interrupt Flag Register<br>Bit 7 6 5<br>0x16 (0xd6) - ICF1<br>ReadWitte R R RW | Bit 7 6 5 4<br>0x16 (0x36) ICF1 -<br>Read/Write R R R/W R | //Counter1 Interrupt Flag Register<br>Bit 7 6 5 4 3<br>Ont6 (kode) 7 6 5 4 3<br>B R RW R R | //Counter1 Interrupt Flag Register           Dit         7         6         4         2           Onte (kode)         7         6         4         3         2           R         R         R         R         R         R         R | //Counter1 Interrupt Flag Register<br>Bi<br>0xts (x06) | r/Counter Interrupt Flag Register           Dit         7         6         4         2         1         0           Ont6 (0049)         -         -         -         -         -         0         0         0         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         1         0         1         1         0         1         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 |

| Prescale Value | Tick Time | OVF<br>frequency            | OVF Period   |

|----------------|-----------|-----------------------------|--------------|

| 1              | 62.5nsec  | ~244.14Hz                   | 4.096msec    |

| 8              | 500nsec   | ~30.52HZ                    | 32.768msec   |

| 64             | 4usec     | ~3.815Hz                    | 262.144msec  |

| 256            | 16usec    | ~0.954Hz                    | ~ 1.05sec    |

| 1024           | 64usec    | ~0.238Hz                    | ~4.19sec     |

|                |           | stem clock f<br>kes to coun | frequency (7 |

| 0         0         No clock source (Timer/Counter stopped).           0         1         clk <sub>v0</sub> /1 (No prescaling)           0         1         0         clk <sub>v0</sub> /84 (From prescale)           0         1         0         clk <sub>v0</sub> /84 (From prescale)           1         0         0         clk <sub>v0</sub> /84 (From prescaler)           1         0         0         clk <sub>v0</sub> /1024 (From prescaler)           1         1         0         Eternal clock source on T pin. Clock on tailing edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CS12 | CS11                          | CS10                         | Description                                                               |              |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------|------------------------------|---------------------------------------------------------------------------|--------------|------|

| 0         1         0         ck <sub>40</sub> /8 (From prescaler)           0         1         1         ck <sub>60</sub> /264 (From prescaler)           1         0         0         ck <sub>60</sub> /265 (From prescaler)           1         0         1         ck <sub>60</sub> /265 (From prescaler)           1         0         1         ck <sub>60</sub> /265 (From prescaler)           1         1         1         ck <sub>60</sub> /265 (From prescaler)           1         1         0         External clock source on T1 pin. Clock on failing edge.           1         1         1         External clock source on T1 pin. Clock on failing edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0    | 0                             | 0                            | No clock source (Timer/Counter stopped).                                  |              |      |

| Image: Control of the contro | 0    | 0                             | 1                            | clk <sub>vo</sub> /1 (No prescaling)                                      |              |      |

| 1         0         0         ckirg/256 (From prescalar)           1         0         1         ckirg/256 (From prescalar)           1         0         1         ckirg/1024 (From prescalar)           1         1         0         External clock source on T1 pin. Clock on falling adge.           1         1         1         External clock source on T1 pin. Clock on falling adge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0    | 1                             | 0                            | clk <sub>VO</sub> /8 (From prescaler)                                     |              |      |

| 1         0         1         clk <sub>ef</sub> /1024 (From prescaler)           1         1         0         External clock source on T1 pin. Clock on failing edge.           1         1         0         External clock source on T1 pin. Clock on failing edge.           1         1         1         External clock source on T1 pin. Clock on rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0    | 1                             | 1                            | clk <sub>V0</sub> /64 (From prescaler)                                    |              |      |

| CR1A - Timer/Counter1 Control Register A     2     wave       0     External clock source on T1 pin. Clock on failing edge.       1     1     1   External clock source on T1 pin. Clock on failing edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1    | 0                             | 0                            | clk <sub>vo</sub> /256 (From prescaler)                                   | -            | -    |

| 1     1     External clock source on T1 pin. Clock on rising edge.         CR1A - Timer/Counter1 Control Register A         CR1A - Timer/Counter1 Control Register A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1    | 0                             | 1                            | clk <sub>VO</sub> /1024 (From prescaler)                                  |              |      |

| CR1A - Timer/Counter1 Control Register A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1    | 1                             | 0                            | External clock source on T1 pin. Clock on falling edge.                   |              |      |

| CR1A - Timer/Counter1 Control Register A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1    | 1                             | 1                            | External clock source on T1 pin, Clock on rising edge,                    | -            |      |

| Bit         7         6         5         4         0         2         0           (0x80)         COMTA1         COMTA1         COMTB1         COMTB1         -         -         wGM11         WGM10         ToOM           Read/Wite         TOW         FDW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |                               |                              |                                                                           |              |      |

| ReadWrite RW RW RW R R RW RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |                               |                              |                                                                           |              |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CR1A | Dit                           |                              | 7 6 5 4 0 2 1                                                             |              |      |