# **Introduction to Embedded Systems**

**CS/ECE 6780/5780**

**Al Davis**

Today's topics:

- ·lab logistics

- ·interrupt synchronization

- ·reentrant code

School of Computing University of Utah

CS 5780

### **Lab Logistics**

- · Lab2 Status

- Wed: 3/11 teams have completed their labs

- » likely due to late handout of Lab 2

- · we were 3 days late in getting it to you

- only fair to give you 3 days extens to o on ake appointment w William to dem lab reports still due at next weeks is

- · BUT other labs will stay on schedule

- · Pre-labs must be done before your lab session

- » most of the Wed. non-finishers didn't do this

- » bottom line

- you won't get pre-lab and actual lab done in time if you don't do the pre-lab prior to your lab session

- Don't just blow off any lab

- » labs are additive

- $\cdot$  e.g. previous lab code will be useful for subsequent labs

- · Schedule through first midterm is on the web

- useful to do the reading before the lecture

CS 5780

### **Interrupts**

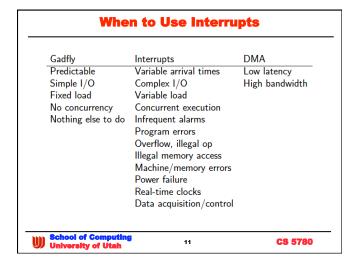

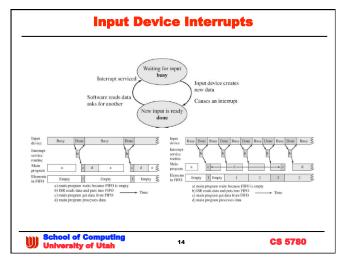

- External wake-up stimulus

- · alternative to the software polling loop

- Efficient response to rare events

- · importance will vary

- » low-power warning → emergency

- » key got pushed → handle soon but not now

- energy efficient

- » processor doesn't consume energy in a polling loop

- » or it can be doing something else that is useful

- Highly useful for data acquisition and control

- Predictable response time?

- · depends on how you configure the system

- · predictability is a MUST in real-time systems

- Interrupts add concurrency to your ES software

- · this can make you life very difficult

CS 5780

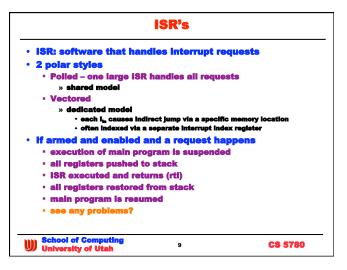

### **What are Interrupts**

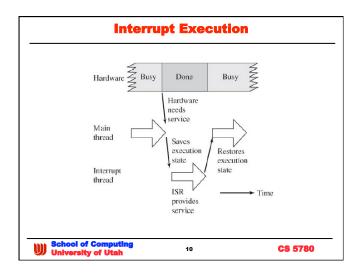

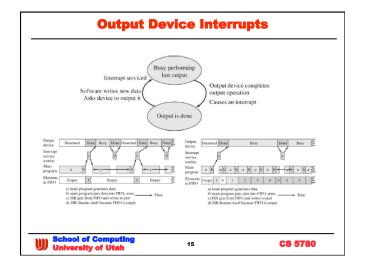

- Automatic hardware supported transfer of control

- external hardware runs asynchronously & concurrently

- » w.r.t. controller SW

- Interrupts transfer control out of whatever is currently running

- » to an interrupt service routine (ISR)

- · looks like a surprise call to the ISR that you write

- d thread · ISR is a 🌬

- » ISR return is done via the rti instruction

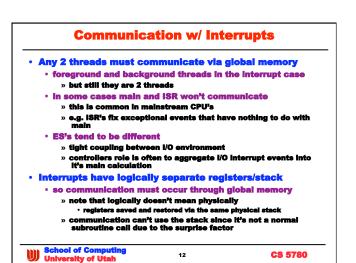

- » Interrupts communicate with main using shared memory

- · concurrency usually requires some form of mutu

- Software interrupts

- these are synchronous

- » SWI instruction (one use would be a breakpoint)

- » automatically happens on 6812 via an unimplem

- e.g. ISR may implement the opcode or send command to off chip implementation

# **Reentrant Programming**

- Program reentrant If

- can be XEQ's by >1 threads of control

- Program must

- place local variables on the stack or use some form of mutual exclusion to prevent conflict on global storage

- Non-reentrant subroutine

- · has a vulnerable window

- · error occurs if

- » main or an ISR calls while running in the vulnerable window

- - » make sure only one active call can be in the vulnerable window

- » mutex mechanisms

- semaphore variable

disable interrupts

CS 5780

### **Reentrant or Not?**

- Must be able to recognize potential sources of bugs

- · due to non-reentrant code in high-level languages

- » just for yucks we'll define C to be high level

- Another example of why you'll sometimes need to examine assembly code

- Is time++ atomic?

- » Yes if compiler generates

- inc time

- » No if compiler generates

- 1dd time

- add #1

- std time

What is the essential difference?

CS 5780

## **Atomic Operations**

- Atomic operation

- · an operation that once started is guaranteed to finish

- In most machines

- a single assembly instruction is atomic

- » If an interrupt happens it will be taken between instructions

- » not during

- Hence

The following is atomic:

inc counter where counter is global variable

The following is *nonatomic*:

ldaa counter where counter is global variable

inca

staa counter

School of Computing University of Utah

19

CS 5780

# **Read-Modify-Write Example**

- Typical case where atomicity is desired

- but not guaranteed ===→ bug time BIG TIME

Software reads global variable, producing a copy of the data.

Software modifies the copy.

Software writes modification back into global variable.

unsigned int Money; /\* bank balance (global) \*//\* add 100 dollars \*/ void more(void){ Money += 100;}

bank balance implemented as a global st add 100 dollars to the account

more 1dd Money where Money is a global variable addd #100 std Money Money=Money+100 rts

School of Computing University of Utah

20

### **Write followed by Read Example**

### RAW hazard

```

Software writes to a global variable.

Software reads from global variable expecting original data.

int temp; /* global temporary */

/* calculate x+2*d */

int mac(int x, int d){

temp = x+2*d; /* write to a global variable */

return (temp);} /* read from global */

temp rmb 2 global temporary result

* calculate RegX=RegX+2*RegD

mac stx temp Save X so that it can be added

lsld RegD=2*RegD

addd temp RegD=RegX+2*RegD

xgdx RegX=RegX+2*RegD

rts

```

University of Utah

School of Computing University of Utah 21

CS 5780

### **Nonatomic Multistep Write**

Software write part of new value to a global variable. Software write rest of new value to a global variable.

School of Computing

CS 5780

# **Disabling Interrupts in C**

```

int Empty; /* -1 means empty, 0 means it contains somethi

int Message; /* data to be communicated */

int SEND(int data){ int OK;

char SaveSP;

asm tpa

asm staa SaveSP

asm sei

/* make atomic, entering critical */

/* Assume it is not OK */

OK=0;

if(Empty){

Message=data;

Empty=0; /* signify it is now contains a message*/

OK=-1;} /* Successfull */

asm ldaa SaveSP

asm tap /* end critical section */

return(OK);}

```

23

# **A Binary Semaphore**

```

* Global parameter: Semi4 is the mem loc to test and set

* If the location is zero, it will set it (make it -1)

* and return Reg CC (Z bit) is 1 for OK

* If location is nonzero, return Reg CC (Z bit) = 0

Semi4 fcb 0 Semaphore is initially free

Tas tst Semi4 check if already set

bne Out busy, operation failed, return Z=0

dec Semi4 signify it is now busy

bita #0 operation successful, return Z=1

Out rts

```

24

School of Computir

CS 5780

# **Interrupt Synchronization Summary**

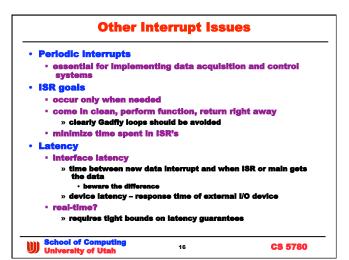

- Device synchronization requires some protocol

to permit HW and SW FSM's to interact

- HW protocols found in the device specifications

- » often cast in concrete

- » SW protocol must be compatible

- Interrupts are essentially a state machine

- · Interaction between main and the ISR follows a protocol

- » supported by hardware

- However

- since you're writing both main and the ISR

you'll be tempted to not think it through carefully

- this is why interrupts are hard

most of us make this mistake on the initial try or two

fortunately mistake enhanced learning works quite well