| Lab Logistics                                                      |                                              |                               |

|--------------------------------------------------------------------|----------------------------------------------|-------------------------------|

| • Lab2 Status                                                      |                                              |                               |

| <ul> <li>Wed: 3/11 teams have</li> </ul>                           | completed their                              | labs                          |

| » likely due to late han                                           | dout of Lab 2                                |                               |

| <ul> <li>we were 3 days late</li> </ul>                            | • • •                                        |                               |

| <ul> <li>only fair to give you</li> </ul>                          | 3 days extension<br>t w/ William to demonstr | -                             |

|                                                                    | e at next weeks lab ses                      |                               |

| <ul> <li>BUT other labs will a</li> </ul>                          | stay on schedule                             |                               |

| <ul> <li>Pre-labs must be done</li> </ul>                          | before your lab                              | session                       |

| » most of the Wed. non                                             | -finishers didn't do                         | ) this                        |

| » bottom line                                                      |                                              |                               |

| <ul> <li>you won't get pre-lai<br/>pre-lab prior to you</li> </ul> |                                              | e in time if you don't do the |

| <ul> <li>Don't just blow off any</li> </ul>                        | lab                                          |                               |

| » labs are additive                                                |                                              |                               |

| <ul> <li>e.g. previous lab cod</li> </ul>                          | le will be useful for s                      | ubsequent labs                |

| Schedule through first                                             | midterm is on t                              | the web                       |

| <ul> <li>useful to do the readin</li> </ul>                        | g before the lec <sup>.</sup>                | ture                          |

| School of Computing<br>University of Utah                          | 2                                            | <b>CS 5780</b>                |

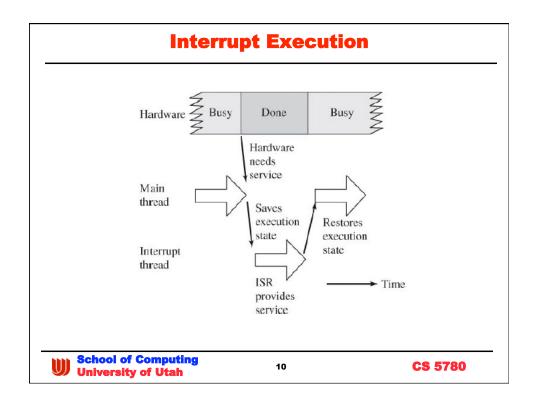

| What are Interrupts                                                                                                                          |                     |          |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|

| Automatic hardware support                                                                                                                   | ed transfer of co   | ntrol    |

| <ul> <li>external hardware runs async</li> <li>» w.r.t. controller SW</li> </ul>                                                             | chronously & conc   | urrently |

| <ul> <li>interrupts transfer control ou<br/>running</li> </ul>                                                                               | t of whatever is cu | irrently |

| <ul> <li>» to an interrupt service routin</li> <li>• looks like a surprise call to t</li> <li>• ISR is a <i>background</i> thread</li> </ul> | · · ·               |          |

| » ISR return is done via the rt:                                                                                                             | instruction         |          |

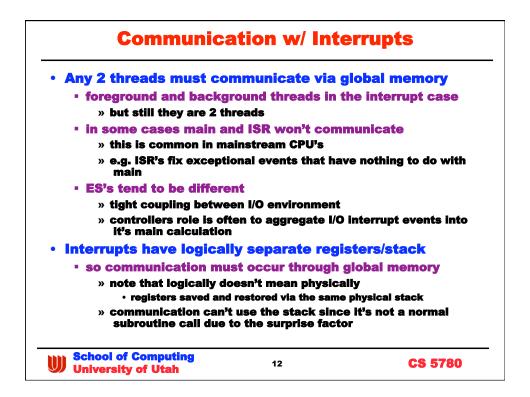

| <ul> <li>interrupts communicate with</li> <li>concurrency usually required</li> <li>such as semaphores</li> </ul>                            | •                   | •        |

| Software interrupts                                                                                                                          |                     |          |

| <ul> <li>these are synchronous</li> </ul>                                                                                                    |                     |          |

| <ul> <li>SWI instruction (one use work automatically happens on 68</li> <li>e.g. ISR may implement the implementation</li> </ul>             | 12 via an unimpleme | -        |

| School of Computing<br>University of Utah                                                                                                    | l                   | CS 5780  |

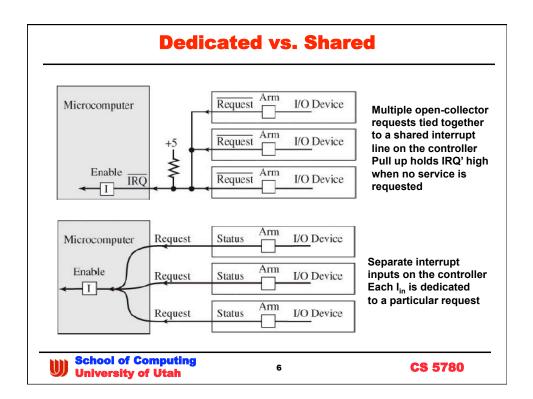

| <b>Dedicated vs. Shared</b>                                                                          |                              |                       |

|------------------------------------------------------------------------------------------------------|------------------------------|-----------------------|

| • Shared                                                                                             |                              |                       |

| +'s use of wired-or style                                                                            | le interrupts (op            | en collector on 6812) |

| » no limit on number of                                                                              | interrupt capable            | devices               |

| » simple hardware and                                                                                | wiring                       |                       |

| » expansion to include                                                                               | more I/O devices             | requires no redesign  |

| • cons:                                                                                              |                              |                       |

| » ISR must look at all p<br>service is required                                                      | oossible device re           | gisters to see what   |

| <ul> <li>there may be more to</li> </ul>                                                             | than one                     |                       |

| » dispatch to appropria                                                                              | nte routine                  |                       |

| » reset the request bit                                                                              |                              |                       |

| <ul> <li>Dedicated</li> </ul>                                                                        |                              |                       |

| +'s: simpler software d                                                                              | lue to dedicated             | ISR's                 |

| <ul> <li>faster since SW does</li> <li>less software couplin</li> <li>easier to implement</li> </ul> | ng                           | everybody             |

| •                                                                                                    |                              |                       |

| <ul> <li>con: you might run out</li> </ul>                                                           | or dedicated I <sub>in</sub> | 3                     |

| School of Computing<br>University of Utah                                                            | 8                            | CS 5780               |

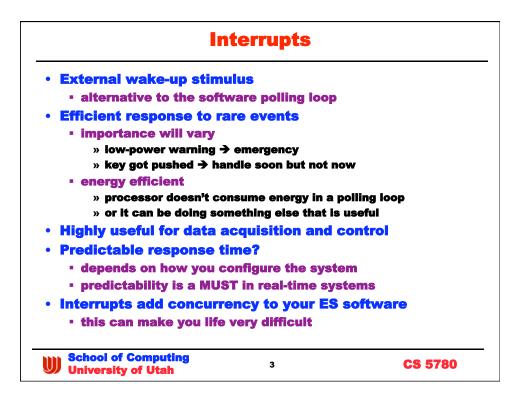

| Gadfly             | Interrupts               | DMA            |

|--------------------|--------------------------|----------------|

| Predictable        | Variable arrival times   | Low latency    |

| Simple I/O         | Complex I/O              | High bandwidth |

| Fixed load         | Variable load            |                |

| No concurrency     | Concurrent execution     |                |

| Nothing else to do | Infrequent alarms        |                |

|                    | Program errors           |                |

|                    | Overflow, illegal op     |                |

|                    | Illegal memory access    |                |

|                    | Machine/memory errors    |                |

|                    | Power failure            |                |

|                    | Real-time clocks         |                |

|                    | Data acquisition/control |                |

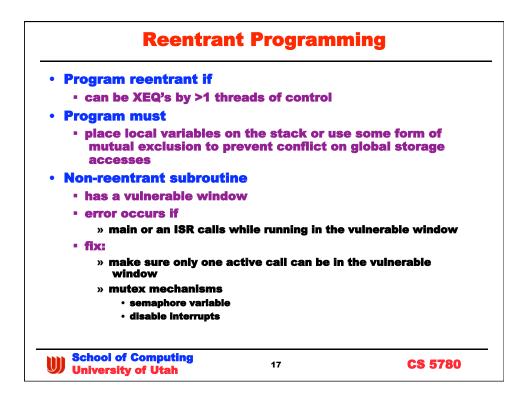

| <b>Other Interrupt Issues</b>                                                                          |                      |                      |

|--------------------------------------------------------------------------------------------------------|----------------------|----------------------|

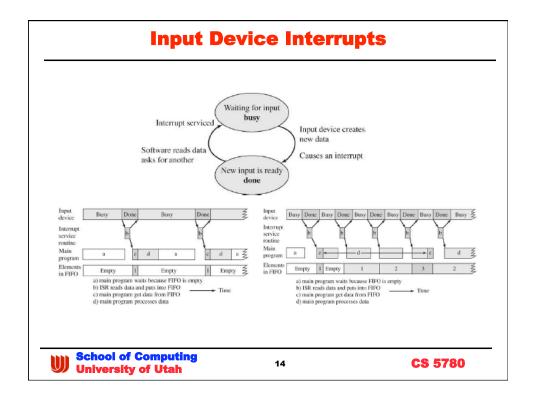

| Periodic interrupts                                                                                    |                      |                      |

| <ul> <li>essential for implementation systems</li> </ul>                                               | enting data acquis   | ition and control    |

| • ISR goals                                                                                            |                      |                      |

| • occur only when nee                                                                                  | ded                  |                      |

| <ul> <li>come in clean, perfor</li> <li>» clearly Gadfly loops</li> <li>minimize time spent</li> </ul> | s should be avoided  | n right away         |

| • Latency                                                                                              |                      |                      |

| <ul> <li>interface latency</li> </ul>                                                                  |                      |                      |

| » time between new (<br>the data<br>• beware the differe                                               | -                    | hen ISR or main gets |

| » device latency – rea                                                                                 | sponse time of exter | nal I/O device       |

| real-time?                                                                                             |                      |                      |

| » requires tight bound                                                                                 | ds on latency guarar | itees                |

| School of Computing<br>University of Utah                                                              | 16                   | CS 5780              |

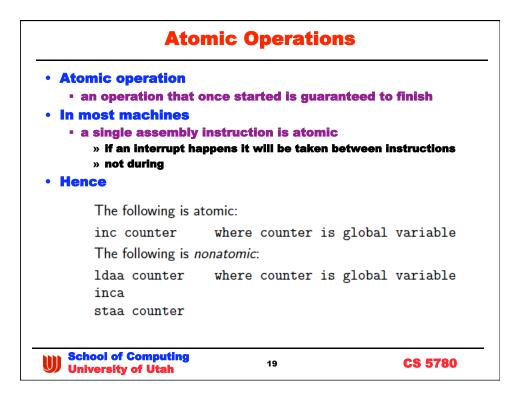

| <b>Reentrant or Not?</b>                                                                 |                      |             |

|------------------------------------------------------------------------------------------|----------------------|-------------|

| Must be able to recogni                                                                  |                      |             |

| <ul> <li>due to non-reentrant construction</li> <li>» just for yucks we'll de</li> </ul> |                      |             |

| Another example of why<br>examine assembly cod                                           | y you'll someti<br>e | mes need to |

| Is time++ atomic?                                                                        |                      |             |

| » Yes if compiler generation                                                             | ates                 |             |

| • inc time                                                                               |                      |             |

| » No if compiler genera                                                                  | tes                  |             |

| • 1dd time                                                                               |                      |             |

| • add #1                                                                                 |                      |             |

| • std time                                                                               |                      |             |

| What is the essential diff                                                               | erence?              |             |

| School of Computing                                                                      | 18                   | CS 5780     |

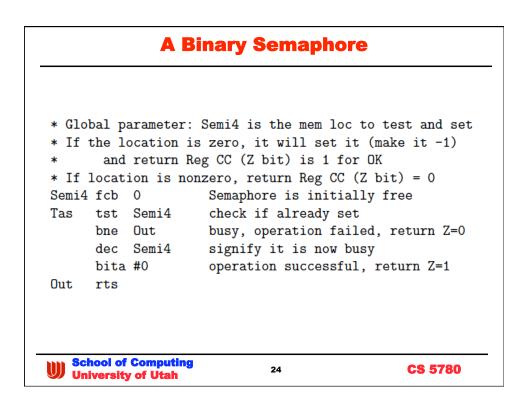

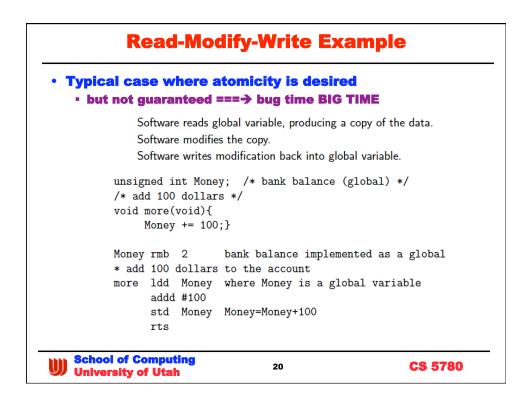

## **Disabling Interrupts in C**

```

/* -1 means empty, 0 means it contains somethi

int Empty;

int Message; /* data to be communicated */

int SEND(int data){ int OK;

char SaveSP;

asm tpa

asm staa SaveSP

asm sei

/* make atomic, entering critical */

OK=0;

/* Assume it is not OK */

if(Empty){

Message=data;

Empty=0; /* signify it is now contains a message*/

OK=-1;}

/* Successfull */

asm 1daa SaveSP

asm tap

/* end critical section */

return(OK);}

School of Computing

23

CS 5780

University of Utah

```