## Introduction to Embedded Systems CS/ECE 6780/5780 Al Davis Today's topics: ·some logistics nagging ·assembly language programming School of Computing 1 CS 5780

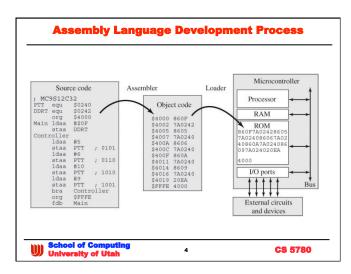

### **6812 Assembly Language** · Details are in references on the web page too boring to enumerate in class so we'll cover the highlights **Addresses and symbols** assembler usually is a 2-pass process » 1: build the symbol table:values map • explicit value - PTT equ \$2040 • Implicit value: label a particular location in the co » 2: create object file based on symbol table phasing error results if symbol value differs between · Result is a listing file · errors are listed if they occur » undefined symbol, illegal opcode, branch distance too far, etc. » symbol table values » hex object code School of Computing University of Utah CS 5780

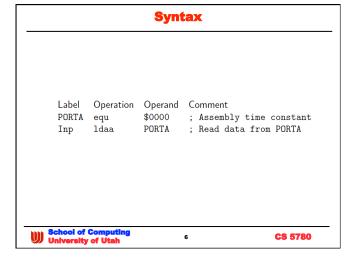

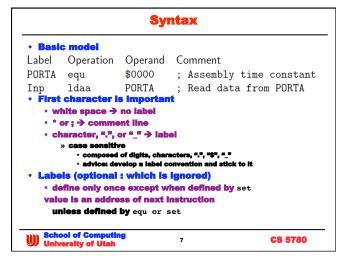

# Operations must be proceeded by at least one white space character, and they are case-insensitive (nop, NOP, NoP). Operations can be an opcode or assembler directive (pseudo-op). Operand must be proceeded by white space. Operands must not contain any white space unless the following comment begins with a semicolon. Operands are composed of symbols or expressions.

| Operand                                     | Format              | Example             |

|---------------------------------------------|---------------------|---------------------|

| no operand                                  | INH                 | clra                |

| # <expression></expression>                 | IMM                 | ldaa #4             |

| <expression></expression>                   | DIR,EXT,REL         | ldaa 4              |

| <expression>,idx</expression>               | indexed (IND)       | ldaa 4,x            |

| <expr>,#<expr></expr></expr>                | bit set or clear    | bset 4,#\$01        |

| <expr>,#<expr>,&lt; expr &gt;</expr></expr> | bit test & branch   | brset 4,#\$01,foo   |

| <expr>,idx,#<expr>,&lt; expr</expr></expr>  | > bit test & branch | brset 4,x,#\$01,foo |

| <expression>,idx+</expression>              | IND, post incr      | ldaa 4,x+           |

| <expression>,idx-</expression>              | IND, post decr      | ldaa 4,x-           |

| <expression>,+idx</expression>              | IND, pre incr       | ldaa 4,+x           |

| <expression>,-idx</expression>              | IND, pre decr       | ldaa 4,-x           |

| acc,idx                                     | accum offset IND    | ldaa A,x            |

| [ <expression>,idx]</expression>            | IND indirect        | ldaa [4,x]          |

| [D,idx]                                     | RegD IND indirect   | ldaa [D,x]          |

### **Building the Object Code**

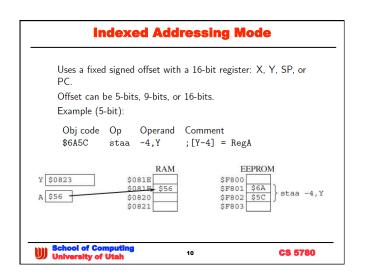

staa -4,Y → \$6A5C

First byte is \$6A - Op code (pg. 254)

Second byte is formatted as %rr0nnnnn (pg. 33).

rr is %01 for register Y.

nnnnn is %11100 for -4.

%0101 1100 → \$5C.

Information is found in the CPU12 Reference Manual (CPU12RM.pdf).

School of Computing University of Utah 11 CS 5780

### **Auto Pre/Post Dec/Inc Indexed Mode**

Can be used with the X, Y, and SP registers, but not PC. The register used is incremented/decremented by the offset value (1 to 8) either before (pre) or after (post) the memory access.

In these examples assume that RegY=2345:

Op Operand Staa 1,Y+ ;Store RegA at 2345, then RegY=2346 staa 4,Y- ;Store RegA at 2345, then RegY=2341 staa 4,+Y ;RegY=2349, then store RegA at 2349 staa 1,-Y ;RegY=2344, then store RegA at 2344

Why not the PC register?

School of Computin University of Utah

### **Building the Object Code**

```

staa 1,X+ → $6A30

First byte is $6A - Op code (pg. 254)

Second byte is formatted as %rr1pnnnn (pg. 33).

rr is %00 for register X.

nnnn is %0000 for 1.

p is %1 for post.

%0011 0000 → $30.

Information is found in the CPU12 Reference Manual (CPU12RM.pdf).

```

CS 5780

### Uses two registers, offset is in A, B, or D, while index is in X, Y, SP, or PC. Examples: Op Operand Comment ldab #4 ldy #2345 staa B,Y; Store value in RegA at 2349

CS 5780

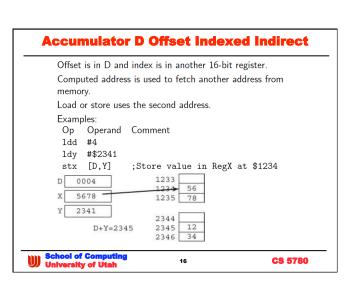

### **Indexed Indirect Mode** Adds 16-bit offset to 16-bit register (X,Y,SP, or PC) to compute address in which to fetch another address. This second address is used by the load or store. Examples: Оp Operand Comment #\$2345 ldy staa [-4,Y] ;Fetch 16-bit address from \$2341, ;store \$56 at \$1234 56 1235 2345 2340 2341 2342 34 School of Computi University of Utah CS 5780 15

### **Load Effective Address**

Used with IND addressing modes.

Calculate the effective address and store it in the specified register:  $X,\,Y,\,$  or SP.

CC bits are not affected.

Example:

leas -4,SP ;SP -=  $4 \rightarrow \$1B9C$  \$1B is leas op code (first byte). Second byte is %rr0nnnn. %10 is the rr code for SP. %1 1100 is -4.

LEAS - load effective address into SP

School of Computing

University of Utah

CS 5780

### **Load and Store Instructions**

- Register ←→ Memory moves

- load instructions: idaa, idab, idd, ids, idx, idy

modes are IMM, DIR, EXT, IND

- store instructions: staa, stab, std, sts, stx, sty

modes are DIR, EXT, IND

- CC N & Z bits updated based on moved value

- Examples

Op Operand Comment ldaa #\$FF TMM staa \$25 DIR ldab \$0025 **EXT** \$05,X IND  $\operatorname{std}$ \$C025 EXT ldd

School of Computing University of Utah

CS 5780

### **M2M Move Instructions**

Move a value from one memory location to another

does not affect the CC register bits

Move an 8-bit constant into memory:

movb #w,addr [addr]=w

Move an 8-bit value memory to memory: movb addr1,addr2 [addr2]=[addr1]

Move a 16-bit constant into memory:

movw #W,addr {addr}=W

Move a 16-bit value memory to memory: movw addr1,addr2 {addr2}={addr1}

19

School of Computing University of Utah

CS 5780

### **Clear/Set Instructions**

Used to initialize memory (clr), accumulators (clra,clrb), or bits in the CC (clc, cli, clv).

clr addressing modes are: EXT, IND.

clra, clrb, clc, cli, clv are INH.

Examples:

Op Operand Comment

clra INH clr \$0025 EXT

The carry (C), interrupt mask (I), and overflow (V) bits in the CC can also be set (sec, sei, sev).

School of Computer University of Literature

20

### **Exchange and Transfer Instructions**

- Transfer (all INH)

- tab: A→ B (also tba)

- tap: A→ CC (also tpa)

- · tsx, txs, tsy, tys, etc. see manual for full set

- Exchange (also INH)

- · double move

- » xgdx, xgdy

CS 5780

### **Add and Subtract**

Registers: aba, abx, aby, sba (all INH).

With carry to memory: adca, adcb, sbca, sbcb.

w/o carry to memory: adda, addb, addd, suba, subb, subd.

Addressing modes are: IMM, DIR, EXT, IND. Examples: 16-bit addition using only A

| Op   | Operand | Comment               |

|------|---------|-----------------------|

| ldaa | \$25    | load least sig byte   |

| adda | \$35    | add data at \$35 to A |

| staa | \$45    | store least sig byte  |

| ldaa | \$24    | load most sig byte    |

| adca | \$34    | add data at \$34 to A |

| staa | \$44    | store most sig byte   |

|      |         |                       |

CS 5780

### **Compare**

Perform a subtraction to update the CC, but do not alter data

Typically used just before a branch instruction.

Compare registers: cba (INH).

Compare to memory: cmpa, cmpb, cpd, cpx, cpy.

Addressing modes: IMM, DIR, EXT, IND Example: comparing with a known set point

Obj code Op Operand Comment

\$8650 ldaa #\$50 load set point into A \$B11031 cmpa \$1031 compare A to memory

23

If Z flag is 1 then the contents of \$1031 equals \$50.

CS 5780

### **Misc. Arithmetic Instructions**

### · Dec/Inc, Negate, Test

dec, deca, decb, des, dex, dey - decrement inc, inca, incb, ins, inx, iny - increment neg, nega, negb - two's complement.

tst, tsta, tstb - subtracts 0 from memory or register and sets Z and N flags in the CC.

24

School of Computi

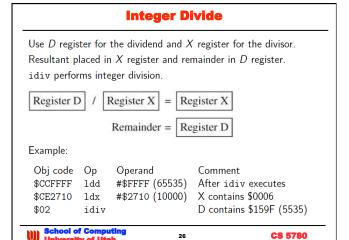

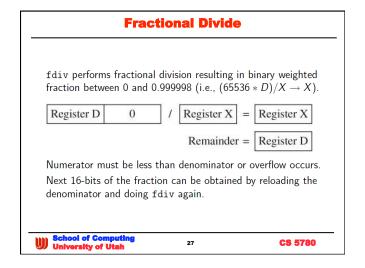

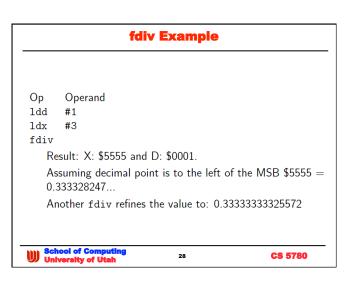

### **Multiply** Multiplies two unsigned 8-bit values in $\boldsymbol{A}$ and $\boldsymbol{B}$ to produce a 16-bit unsigned product stored in D (i.e., $A \times B \rightarrow D$ ). Register D Register A Register B = Register A Register B 8 bits 8 bits 16 bits Example: Op Operand Comment ldaa #\$FF (255) IMM ldab #\$14 (20) INH mul At the end, accumulator D contains \$13EC (5100). \$FF \* \$FF = \$FE01 CS 5780

### **Bitwise Logical Operations**

AND - anda, andb (IMM, DIR, EXT, IND). Inclusive OR - oraa, orab (IMM, DIR, EXT, IND).

Exclusive OR - eora, eorb (IMM, DIR, EXT, IND).

1's complement - com, coma, comb. Example: masking unwanted bits

Obj code Op Operand Comment \$8634 ldaa #\$34 %00110100 \$840F anda #\$0F %00001111

Result in A is %00000100

CS 5780

### Bit Test, Set, & Clear

bita and bitb instructions perform an AND operation and update N and Z flags of the CC w/o altering the operand. bclr and bset instructions are used to clear or set bit(s) in a given memory location.

> bclr addr, mm bset addr, mm

where addr is a memory location specified using DIR, EXT, or IND addressing mode and mm is a mask byte.

CS 5780

### Stack Instructions

Stack pointer (RegSP) defines the top of the stack.

Should be loaded with a RAM memory address early in any assembly language program.

Push and pull instructions put data onto and take data off the stack.

psha, pshb, pshx, pshy, pula, pulb, pulx, puly (all INH).

REMEMBER: stack grows down (lower address value)

35

School of Computing University of Utah

CS 5780

### **Subroutine Linkage (Manual)**

Op Comment Callee saves state to stack pshy INH Restores state on return pshx INH pshb INH psha INH INH tpa psha INH body of subroutine pula INH tap pula TNH pulb INH pulx INH puly INH

School of Cor University of

36

### **Subroutine Call and Return**

bsr - branch to subroutine using REL addressing.

jsr - jumps to subroutine using DIR, EXT, or IND addressing.

On either bsr or jsr, PC is automatically pushed onto the

stack (least significant byte first).

${\tt rts}$  - return from subroutine, PC automatically pulled off the stack and jumps to that location.

bsr offset is 8-bit signed value

School of Computir University of Utah CS 5780

### **Jump, Branch, Branch Always**

jmp and bra instructions are unconditional.

bra uses relative addressing (REL) so it can only be used to jump -128 or 127 instructions.

jmp can use EXT and IND addressing so it can be used to jump anywhere in the 64K address space.

bra \$ stops progress of CPU, but it continues to execute this instruction.

School of Computing

8

CS 5780

### **Single Condition Branches**

bcc - branch if carry clear (i.e., C = 0).

bcs - branch if carry set (i.e., C = 1).

bne - branch if not equal to zero (i.e., Z = 0).

beq - branch if equal to zero (i.e., Z = 1).

bpl - branch if positive or zero (i.e., N = 0).

bmi - branch if negative (i.e., N = 1).

bvc - branch if overflow clear (i.e., V = 0).

bvs - branch if overflow set (i.e., V = 1).

brn - branch never hard to say what this is good for

School of Computing University of Utah

39

CS 5780

### **Example: Equality Tests**

```

C Code

Assembly Code

if (G2==G1) {

1daa G2

isEqual();

cmpa G1

bne next

; skip if not equal

jsr isEqual ;G2==G1

next

if (G2!=G1) {

ldaa G2

isNotEqual();

cmpa G1

beq next

;skip if equal

jsr isNotEqual ;G2!=G1

next

```

School of Computin University of Lifeh

4

### **Unsigned Number Branches**

```

These branches usually follow cba, cmp(A,B,D), cp(X,Y),

sba, sub(A,B,D) instructions.

bhi - branch if higher '>' (i.e., C + Z = 0).

bhs - branch if higher or same '\geq ' (i.e., C=0).

blo - branch if lower '<' (i.e., C=1).

bls - branch if lower or same '\leq' (i.e., C + Z = 1).

```

CS 5780

### **Signed Number Branches**

These branches usually follow cba, cmp(A,B,D), cp(X,Y), sba, sub(A,B,D) instructions.

bgt - branch if greater '>' (i.e.,  $Z + (N \oplus V) = 0$ ).

bge - branch if greater or equal ' $\geq$ ' (i.e.,  $N \oplus V = 0$ ).

blt - branch if less '<' (i.e.,  $N \oplus V = 1$ ).

ble - branch if less or equal ' $\leq$ ' (i.e.,  $Z + (N \oplus V) = 1$ ).

CS 5780

### **Example: Unsigned Tests**

```

C Code

Assembly Code

_____

unsigned int G1;

ldaa G2

unsigned int G2;

cmpa G1

if (G2 > G1) {

bls next

;skip if G2<=G1

isGreater();

jsr isGreater ;G2>G1

next

unsigned int G1;

ldaa G2

unsigned int G2;

cmpa G1

;skip if G2<G1

if (G2 > G1) {

blo next

isGreaterEq();

jsr isGreaterEq ;G2>=G1

}

next

```

43

School of Computing University of Utah

CS 5780

### **Miscellaneous But Useful**

nop — no operation, creates a 2-cycle delay.

swi — trigger a software interrupt.

rti — called at the end of an interrupt service routine to restore the CPU registers.

wai — puts CPU into standby mode waiting for an interrupt; CPU clock is stopped but other MCU clocks can continue to

stop — stop all clocks to save power; start on  $\overline{RESET}$ ,  $\overline{XIRQ}$ , or unmasked  $\overline{IRQ}$ ; RAM, I/O space, and registers are preserved.

44

School of Computi

### **Assembler Pseudo-Ops**

Reserve multiple 32-bit words (ds.1, .blk1):

<label> ds.1 <expression>

CS 5780

### **More Pseudo-Ops**

Form constant byte (fcb, dc.b, db, .byte):

<label> fcb <expression>

Form double byte (fdb, dc.w, dw, .word):

<label> fdb <expression>

Define 32-bit constant (dc.1, dl, .long):

<label> fqb <expression>

Form constant character string (fcc):

hello fcc ''Hello World'',0

School of Computing University of Utah

CS 5780

### **Concluding Remarks**

- Boring and still incomplete

- hopefully you have background to read understand the ISA & assembler

- » read the reference documentation for the whole scoop

- Addressing modes are the key to reading and writing assembly

- · you'll tend to read it more than write → debug

- write usually only happens when you need low-level HW control

- · condition codes and subsequent branches are important

- » Ignore and bugs appear

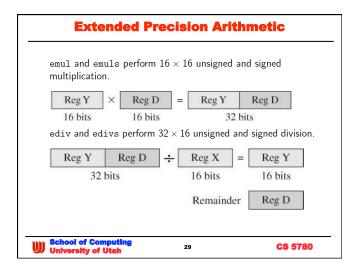

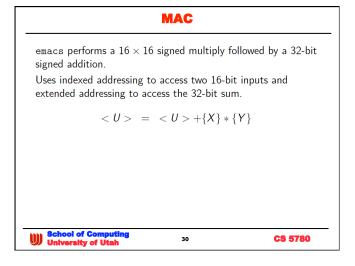

- Extensive math support

- for operations wider than 8 bits

- **Assembly coding is hard**

- easy to make basic and serious mistakes

- » save & restore state, mis-matched stack frames, CC screw-ups

- » Pandora's box in a way

School of Computing University of Utah

47