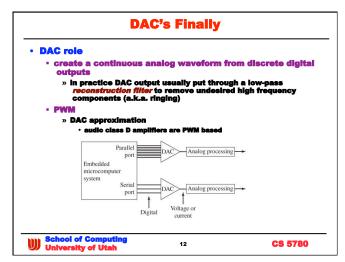

# CS/ECE 6780/5780 Al Davis Today's topics: • Midterm 2 hints • no practice midterm since it didn't help last time • ADC's and DAC's • chapter 11 of your text • your kit has an A/D (Port D w/ DDR set to inputs) • handy since sensors often supply analog value • your kit doesn't have a D/A • sometimes needed for analog control of external devices (e.g. VF converters) • which I was hoping to have as a lab (alas) School of Computing University of Utah

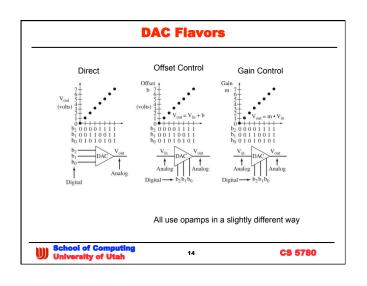

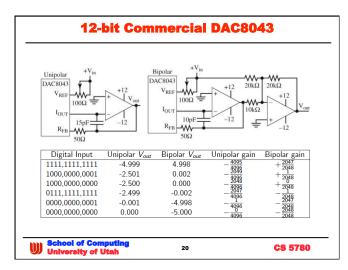

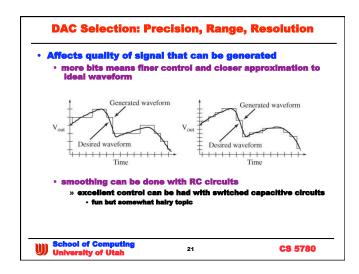

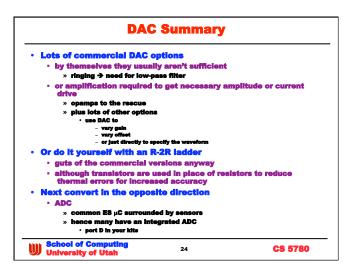

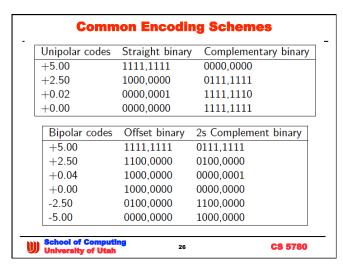

## Precision - # of distinguishable DAC outputs • Range - min to max of output values • Resolution - smallest distinguishable change in output Range (volts) = Precision (alternatives) · Resolution (volts) • 2 common encoding schemes 2's complement and 1's complement $V_{out} = V_{ls} \left( \frac{b_f}{2} + \frac{b_h}{4} + \frac{b_3}{8} + \frac{b_h}{16} + \frac{b_2}{32} + \frac{b_1}{64} + \frac{b_1}{128} + \frac{b_0}{256} \right) + V_{os}$ $V_{out} = V_{ls} \left( -\frac{b_7}{2} + \frac{b_8}{4} + \frac{b_8}{8} + \frac{b_4}{16} + \frac{b_3}{32} + \frac{b_1}{64} + \frac{b_1}{128} + \frac{b_0}{256} \right) + V_{os}$ Vos = output offset voltage

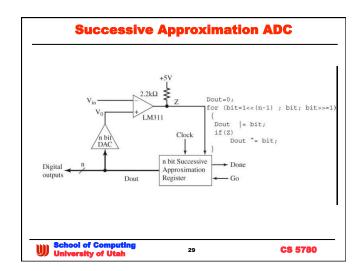

## **6812 Internal ADC** • Eight channel operation 8 or 10-bit resolution • Successive approximation technique Clock and charge pump to create higher voltages • 2 operation modes • single sequence and stop

- multiple conversions of single channel · or one conversion each for a group of channels

- External reference voltages · Vrh - high reference

- · Vri low reference

- continuous

Supports

CS 5780

### 6812 ADC Setup

- Port AD input configurations

- 8 pins individually configured for anolog or digital input

- » ATDDIEN register

- · 1 = digital, 0 = analog

- If ATTDIEN indicates digital

- » then DDRAD register is used to set direction

- SRES8 (ATDCTL4[7]) register selects resolution

- » 1 → 8-bit, 0→ 10-bit

- ATDCTL2 register

- » [7] = ADPU set to 1 to enable ADC system

- » [1] = ASCIE set to 1 to enable/arm interrupts

- » [0] = ASCIF set by ADC to 1 when sequence comple · only works If ASCIE is set

CS 5780

CS 5780

### **6812 ADC Conversions**

- When triggered

- 1-8 conversions are performed

- » # = value in ATDCTL3[6:3]

- · Channel selection

- · ATDCTL5[2:0]= CC,CB,CA

- Multiple channels

- set ATDCTL5[4] = 1

- sequence set by ATDCTL3[6:3] start here and cycle

- · each channel has separate completion flag

- » ATDSTAT1 register (8 bits)

- » ATDSTAT0[2:0] counter which shows conversion progress

### **6812 ADC Triggers**

- Triggered in 3 ways

- explicit software write to ATDCTL5 when interrupts armed

- · continuous if SCAN = ATDCTL5[5] is 1

- external trigger if ETRIG = ATDCTL2[2] is 1

- » in this case ETRIGLE & ETRIGP controls what the trigger is

| ETRIGLE | ETRIGP | External trigger mode      |  |

|---------|--------|----------------------------|--|

| 0       | 0      | Falling edge of PAD7       |  |

| 0       | 1      | Rising edge of PAD7        |  |

| 1       | 0      | Convert while PAD7 is low  |  |

| 1       | 1      | Convert while PAD7 is high |  |

School of Computing University of Utah 40

### **6812 ADC Sample Period**

- 2 phase sample

- 1st phase transfer sample to S/H

- · 2<sup>nd</sup> phase attaches external signal to S/H

- E clock and ATDCTL4 control

- SMP1 & SMP2 ATDCTL4[6:5]

| SMP1 | SMP0 | First sample | Second sample | Total         |

|------|------|--------------|---------------|---------------|

| 0    | 0    | 2 ADC clocks | 2 ADC clocks  | 4 ADC clocks  |

| 0    | 1    | 2 ADC clocks | 4 ADC clocks  | 6 ADC clocks  |

| 1    | 0    | 2 ADC clocks | 8 ADC clocks  | 10 ADC clocks |

| 1    | 1    | 2 ADC clocks | 16 ADC clocks | 18 ADC clocks |

• If m is a 5 bit number ATDCTL4[4:0] &  $f_{\rm E}$  is E clock then

ATD clock frequency

$$= \frac{1}{2} \frac{f_E}{(m+1)}$$

School of Computing University of Utah

CS 5780

### **6812 ADC Results**

- Up to 8 samples

- stored in 8 16-bit registers ATDDR0:ATDDR7

- » results can be signed or unsigned

- DSGN = ATDCTL5[6] 1 for signed, 0 for a

- 1 for signed, 0 for unsigned

» right or left justified in the 16-bit register

- · DJM = ATDCTL5[7]

- 1 for right justi

| Input (V) | 8-bit(u) | 10-bit(ur) | 10-bit (ul) | 10-bit (sr) | 10-bit (sl) |

|-----------|----------|------------|-------------|-------------|-------------|

| 0.000     | \$00     | \$0000     | \$0000      | \$FE00      | \$8000      |

| 0.005     | \$00     | \$0001     | \$0040      | \$FE01      | \$8040      |

| 0.020     | \$01     | \$0004     | \$0100      | \$FE04      | \$8100      |

| 2.500     | \$80     | \$0200     | \$8000      | \$0000      | \$0000      |

| 3.750     | \$C0     | \$0300     | \$C000      | \$0100      | \$4000      |

| 5.000     | \$FF     | \$03FF     | \$FFC0      | \$01FF      | \$7FC0      |

School of Computing University of Utah

CS 5780

### **ADC Software Example**

• SW trigger and Gadfly loop

```

void ADC_Init(void){

ATDCTL2 = 0x80; // enable ADC

ATDCTL3 = 0x08;

ATDCTL4 = 0x05; // 10-bit, divide by 12

unsigned short ADC_In(unsigned short chan){

ATDCTL5 = (unsigned char)chan; // start sequence while((ATDSTAT1&0x01)==0){}; // wait for CCF0

return ATDDRO;

```

School of Computing University of Utah

43

CS 5780

### **Concluding Remarks**

- Whiriwind tour for sure

- · like everything in this course

- » learn by experimenting in the lab

- » lecture is HOPEFULLY just a conceptual start

- · can't possibly cover every detail or it would be MORE boring

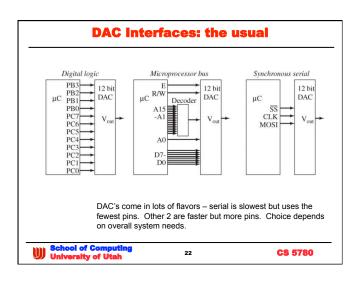

- ADC and DAC

- Integral part of ES life

- » PWM is good for some things

- » more direct analog reading or control is required for others

- midterm2

- » no lab on this stuff so conceptual questions only

- » you should understand the basics without having to look them

- look up is good for nitty gritty details

you'll know them by heart once you've fialled in the lab long en

- **Midterm next Tuesday**

- don't be late

School of Computing University of Utah

44

CS 5780