| Midterm #2                                                                 |                                                        |                          |  |  |

|----------------------------------------------------------------------------|--------------------------------------------------------|--------------------------|--|--|

| • Focus                                                                    |                                                        |                          |  |  |

| <ul> <li>primarily on material cov</li> </ul>                              | vered after the firs                                   | t midterm                |  |  |

| » note I'm not a fan of the                                                | e cram and forget mo                                   | de                       |  |  |

| • unhealthy attitude in a                                                  |                                                        |                          |  |  |

| • nence some (~10%) ma<br>» style likely to be simila                      | • ••                                                   | om pre-midterm1 material |  |  |

| <ul> <li>focus on foundational</li> </ul>                                  |                                                        |                          |  |  |

| <ul> <li>"write a bunch of code</li> <li>but you did this in</li> </ul>    | " problems are good for<br>the labs – so what's the po |                          |  |  |

| <ul> <li>open book and open no</li> <li>danger – If you have to</li> </ul> |                                                        | you'll lose              |  |  |

| • Post midterm1 material                                                   |                                                        |                          |  |  |

| <ul> <li>semaphores and threads</li> </ul>                                 | 1                                                      |                          |  |  |

| <ul> <li>input capture and output</li> </ul>                               | compare                                                |                          |  |  |

| serial I/O: SCI, SPI, UAR1                                                 | r <b>, RS232</b>                                       |                          |  |  |

| <ul> <li>relays and motors, stepp</li> </ul>                               | er motor control                                       |                          |  |  |

| memory: SRAM, DRAM, N                                                      | IVRAM                                                  |                          |  |  |

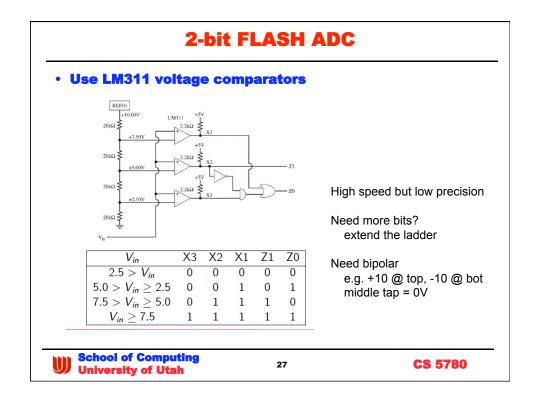

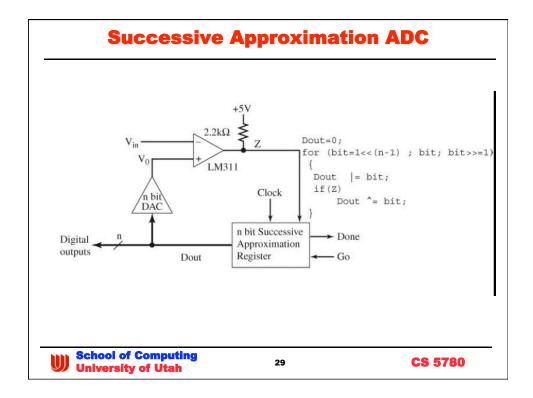

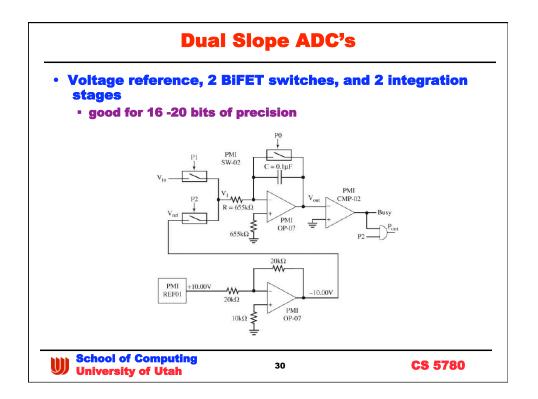

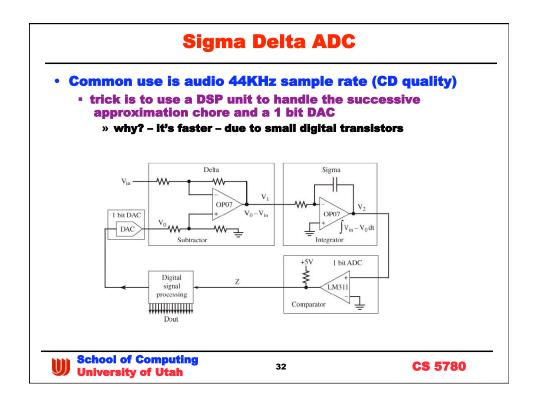

| - ADC & DAC                                                                |                                                        |                          |  |  |

| • All are fair game! (bool                                                 | k, lectures, & l                                       | abs)                     |  |  |

| School of Computing<br>University of Utah                                  | 2                                                      | <b>CS 5780</b>           |  |  |

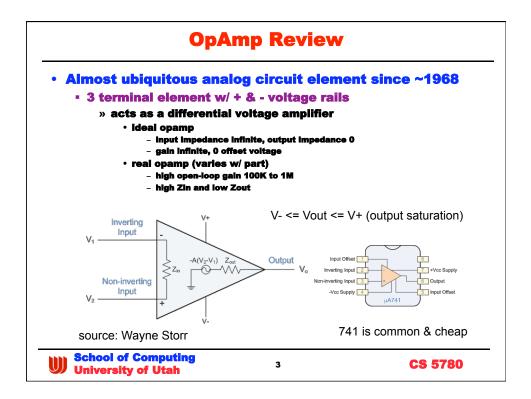

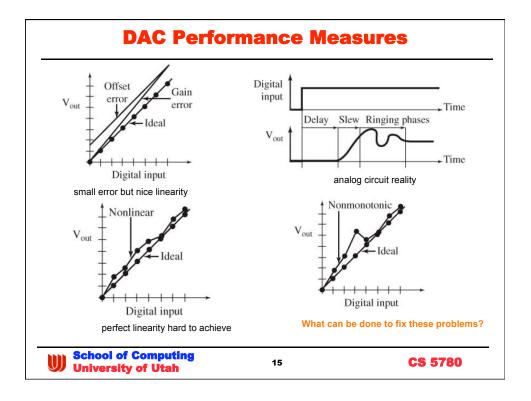

| Errors can be due to              | Solutions                       |  |  |

|-----------------------------------|---------------------------------|--|--|

| Incorrect resistor values         | Precision resistors             |  |  |

|                                   | w/low tolerances                |  |  |

| Drift in resistor values          | Precision resistors             |  |  |

|                                   | w/good temperature coefficients |  |  |

| White noise                       | Reduce BW w/low pass filter,    |  |  |

|                                   | reduce temperature              |  |  |

| Op amp errors                     | Use more expensive devices      |  |  |

|                                   | w/low noise and low drift       |  |  |

| Interference from external fields | Shielding, ground planes        |  |  |

|                                   |                                 |  |  |

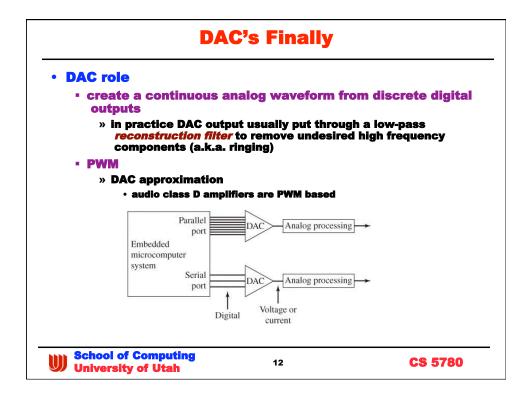

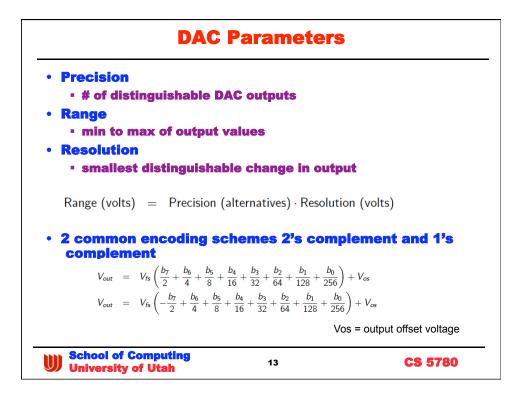

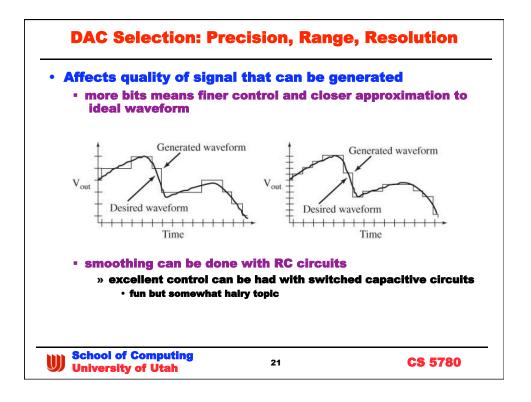

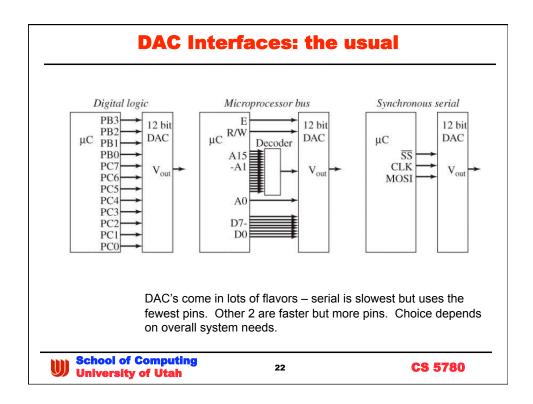

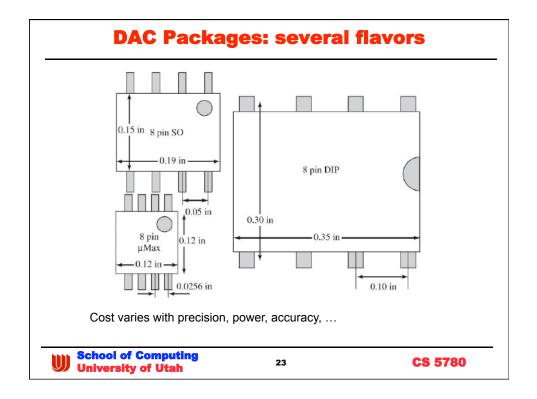

| DAC Summary                                                                                                                                                                                         |                            |                      |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------|--|

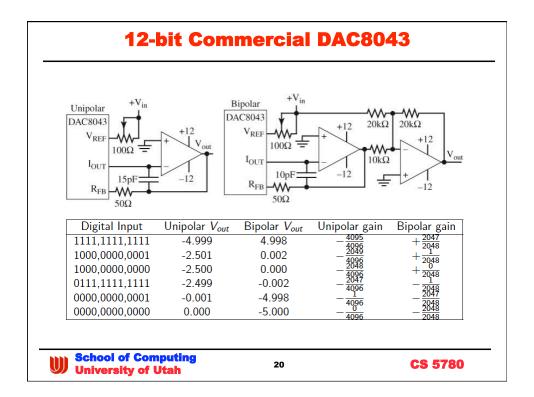

| Lots of commercial DAC                                                                                                                                                                              | options                    |                      |  |

| <ul> <li>by themselves they usuan<br/>» ringing → need for low-</li> </ul>                                                                                                                          | ally aren't sufficient     | E                    |  |

| <ul> <li>or amplification required<br/>drive</li> </ul>                                                                                                                                             | d to get necessary a       | amplitude or current |  |

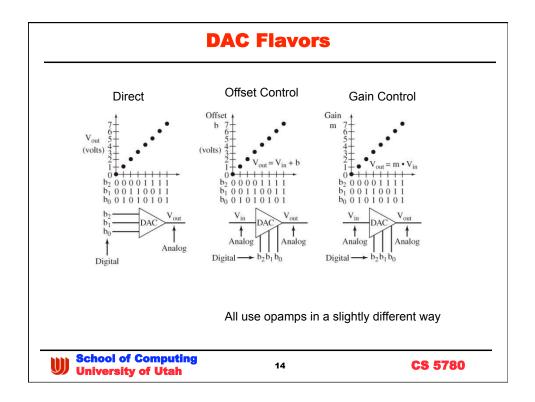

| <ul> <li>» opamps to the rescue</li> <li>» plus lots of other optio</li> <li>• use DAC to         <ul> <li>- vary gain</li> <li>- vary offset</li> <li>- or just directly to</li> </ul> </li> </ul> | ns<br>specify the waveform |                      |  |

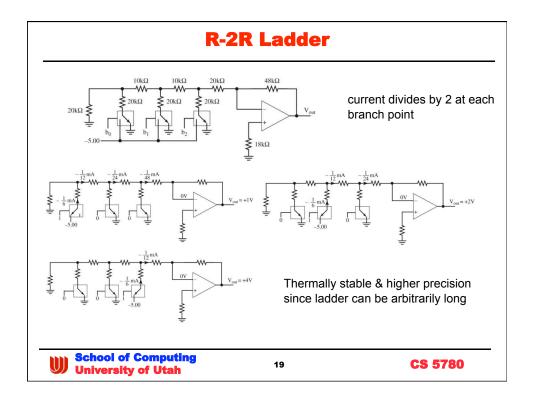

| • Or do it yourself with an                                                                                                                                                                         | <b>R-2R ladder</b>         |                      |  |

| <ul> <li>guts of the commercial</li> </ul>                                                                                                                                                          | versions anyway            |                      |  |

| <ul> <li>although transistors are<br/>thermal errors for incre</li> </ul>                                                                                                                           |                            | sistors to reduce    |  |

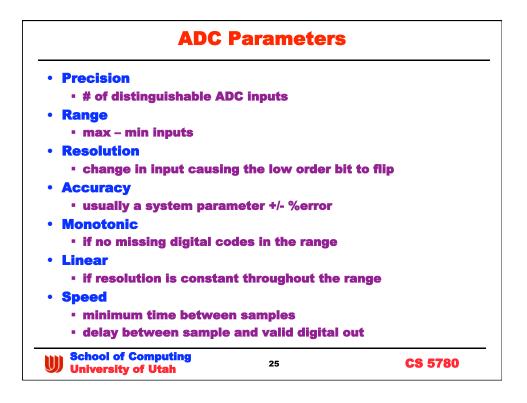

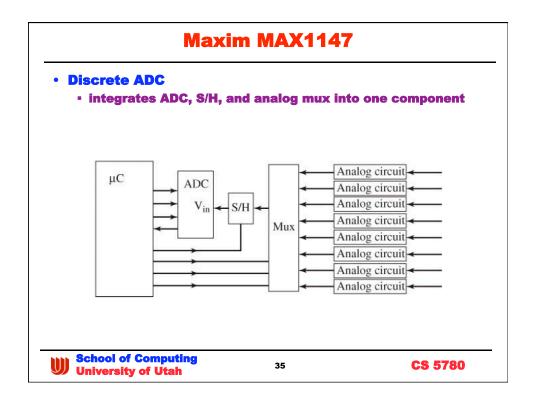

| <ul> <li>Next convert in the oppo</li> <li>ADC         <ul> <li>common ES μC surroun</li> <li>hence many have an in</li> <li>port D in your kits</li> </ul> </li> </ul>                             | nded by sensors            |                      |  |

| School of Computing<br>University of Utah                                                                                                                                                           | 24                         | <b>CS 5780</b>       |  |

| Unipolar codes | Straight binary | Complementary binary |  |

|----------------|-----------------|----------------------|--|

| +5.00          | 1111,1111       | 0000,0000            |  |

| +2.50          | 1000,0000       | 0111,1111            |  |

| +0.02          | 0000,0001       | 1111,1110            |  |

| +0.00          | 0000,0000       | 1111,1111            |  |

| Bipolar codes  | Offset binary   | 2s Complement binary |  |

| +5.00          | 1111,1111       | 0111,1111            |  |

| +2.50          | 1100,0000       | 0100,0000            |  |

| +0.04          | 1000,0000       | 0000,0001            |  |

| +0.00          | 1000,0000       | 0000,0000            |  |

| -2.50          | 0100,0000       | 1100,0000            |  |

| -5.00          | 0000,0000       | 1000,0000            |  |

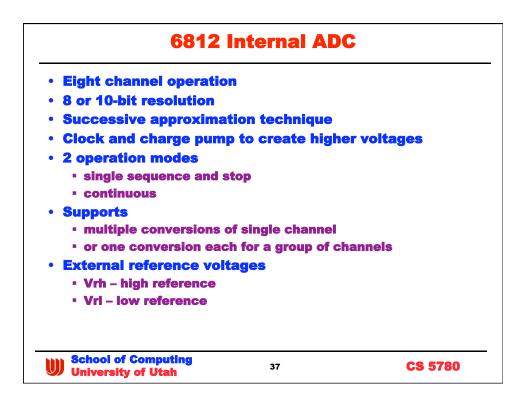

| 6812 ADC Setup |                                                                           |                     |                    |

|----------------|---------------------------------------------------------------------------|---------------------|--------------------|

| ·P             | ort AD input configur                                                     | ations              |                    |

|                | • 8 pins individually co                                                  | nfigured for anolo  | g or digital input |

|                | » ATDDIEN register                                                        |                     |                    |

|                | • 1 = digital, 0 = ana                                                    |                     |                    |

|                | If ATTDIEN indicates                                                      | -                   |                    |

|                | » then DDRAD registe                                                      |                     |                    |

|                | SRES8 (ATDCTL4[7])                                                        | register selects r  | esolution          |

|                | » 1 → 8-bit, 0→ 10-bit                                                    |                     |                    |

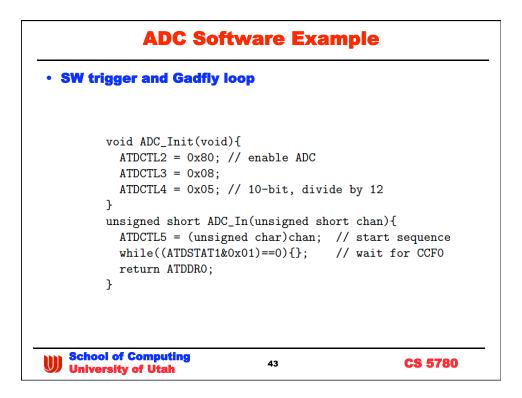

|                | <ul> <li>ATDCTL2 register</li> <li>» [7] = ADPU – set to 1</li> </ul>     | l to onable ADC eve | tom                |

|                | » [1] = ASCIE – set to                                                    | •                   |                    |

|                | <ul> <li>» [0] = ASCIF – set by</li> <li>• only works if ASCII</li> </ul> | ADC to 1 when seq   | •                  |

|                | School of Computing<br>Jniversity of Utah                                 | 38                  | <b>CS 5780</b>     |

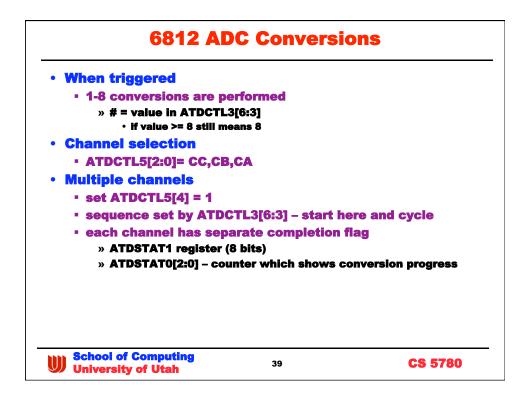

| <ul> <li>continuous i</li> <li>external trig</li> </ul> | ware write (<br>f SCAN = A1<br>ger if ETRIC | to ATDCTL5 when in<br>FDCTL5[5] is 1<br>= ATDCTL2[2] is 1<br>& ETRIGP controls wh |      |

|---------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------|------|

| ETRIGLE                                                 | ETRIGP                                      | External trigger                                                                  | mode |

| 0                                                       | 0                                           | Falling edge of F                                                                 | PAD7 |

| 0                                                       | 1                                           | Rising edge of PAD7                                                               |      |

| 1                                                       | 0                                           | Convert while PAD7 is low                                                         |      |

| 1                                                       | 1                                           | Convert while PAD7 is high                                                        |      |

| School of Comp                                          | 41                                          |                                                                                   |      |

| op to o a                  | amples    | 5               |             |             |             |

|----------------------------|-----------|-----------------|-------------|-------------|-------------|

| <ul> <li>stored</li> </ul> | in 8 16-  | bit regist      | ers ATDD    | RO:ATDDF    | 27          |

| » res                      | uits can  | be signed       | or unsigned | d           |             |

| •                          | DSGN = A  | TDCTL5[6]       | •           |             |             |

|                            |           | signed, 0 for u | •           |             |             |

| •                          |           |                 | the 16-bit  | register    |             |

| •                          | DJM = AT  |                 |             |             |             |

|                            | - 1 for I | ight justified, | 0 for left  |             |             |

| Input (V)                  | 8-bit(u)  | 10-bit(ur)      | 10-bit (ul) | 10-bit (sr) | 10-bit (sl) |

| 0.000                      | \$00      | \$0000          | \$0000      | \$FE00      | \$8000      |

| 0.005                      | \$00      | \$0001          | \$0040      | \$FE01      | \$8040      |

| 0.020                      | \$01      | \$0004          | \$0100      | \$FE04      | \$8100      |

| 2.500                      | \$80      | \$0200          | \$8000      | \$0000      | \$0000      |

| 3.750                      | \$C0      | \$0300          | \$C000      | \$0100      | \$4000      |

|                            | \$FF      | \$03FF          | \$FFC0      | \$01FF      | \$7FC0      |

| 5.000                      |           |                 |             |             |             |

| 5.000                      |           |                 |             |             |             |