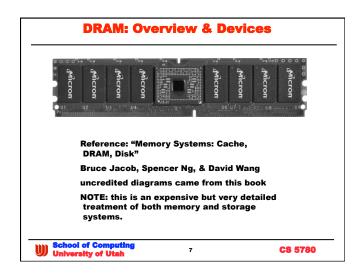

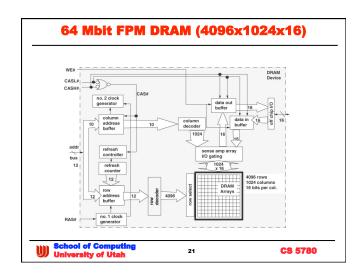

# CS/ECE 6780/5780 Al Davis Today's topics: • External memory • overview of options • brief SRAM introduction • more detailed DRAM intro • mostly we'll care about DRAM chips • some DIMM coverage for added scope School of Computing University of Utah 1 CS 5780

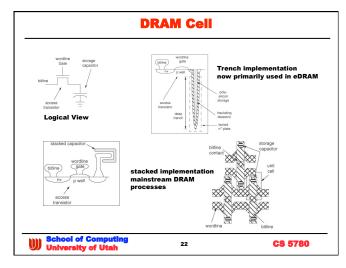

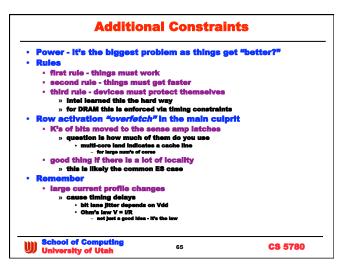

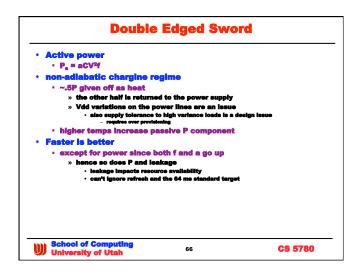

### **Adding Memory Capacity** · Inherent microcontroller problem · limited amount of RAM & FLASH » code tends to not change and be rather small · pick microcontroller w/ enough FLASH to hold your code » so far your data has also been small and fits in RAM » what happens if you have lots of data non issue with data acquisition syste • External memory choices SRAM – fast and easy to interface » problems: expensive, power hungry, volatile DRAM – lots of cheap bits » problems: difficult interface, volatile NVRAM (NV=nonvolatile) » e.g. FLASH but other technologies exist that likely will replace FLASH » pro's: cheap & non-volatile, low power if low usage » con's: interface difficulty varies with technology

CS 5780

School of Computing University of Utah

### **SRAMs** • Typically based on a 6T cell cross coupled inverters hold value as long as there is power · Read – precharge BL's to mid-voltage, activate WL $\ensuremath{\text{\textbf{y}}}$ sense amps detect swing and value is latched to the output · Write drive BL's to the rall, activate WL » note BL drivers must overpower cell translators • so translator sizing is critical to proper operation School of Computing University of Utah CS 5780

CS 5780

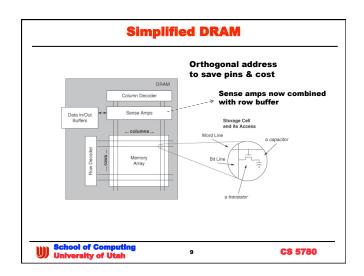

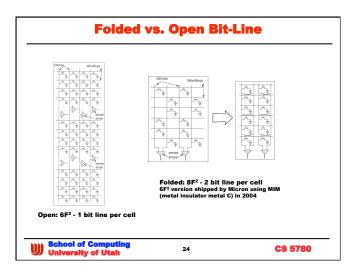

# Open requires dummy array segments at mat edge » balance C characteristics of bit-line pairs more noise susceptibility combine to dilute the cell size advantage Folded differential sense amps have better common-mode noise rejection properties » e.g. alpha particle or neutron spike shows up on both sides current industry focus » new folding strategies show up regularly in circuit venues School of Computing University of Utah 25 CS 5780

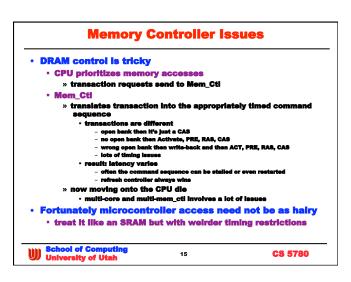

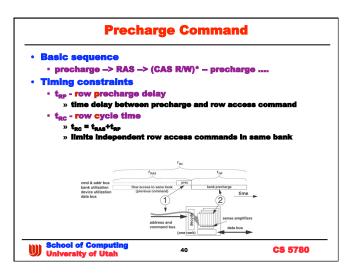

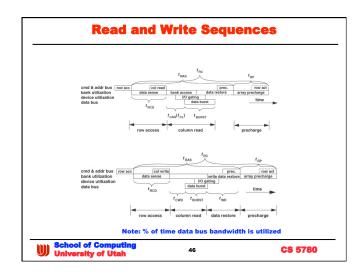

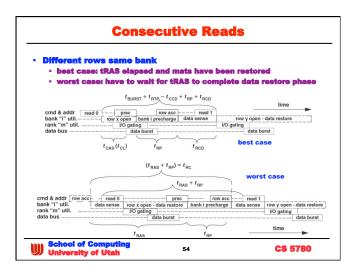

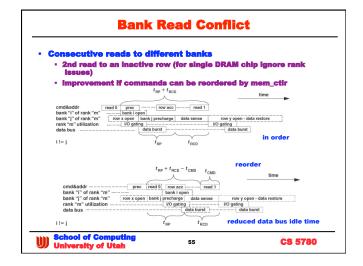

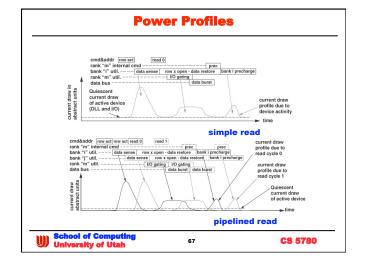

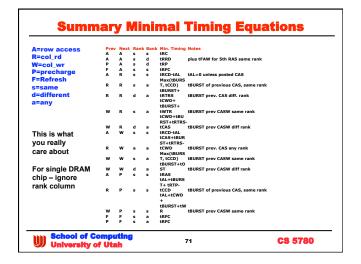

## Significant performance variation Best case read everything in a row and move to next row 1-2 kB in a row - lots of energy expended pass 64-128 B cache-lines to the mem\_ctr access all 8-32 cache lines before opening another row in same bank low probability cache page memory systems - typical keep row buffer open hoping for the best windditional energy cost Worst case Precharge -> RAS -> single CAS -> precharge .... closed page memory systems expect the worst but why not make the row smaller? School of Computing University of Utah 45 CS 5780

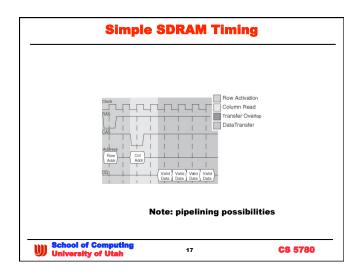

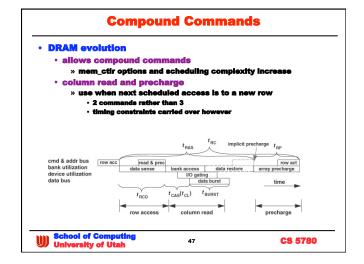

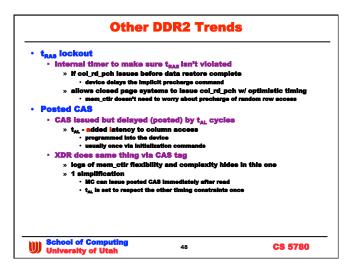

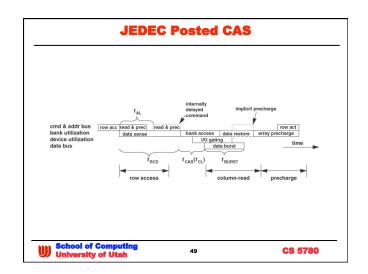

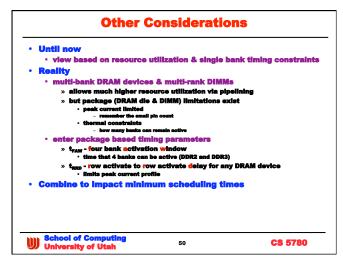

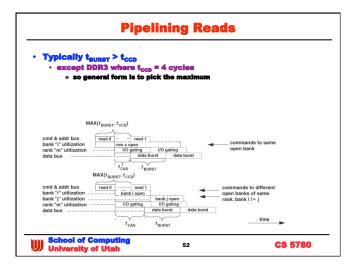

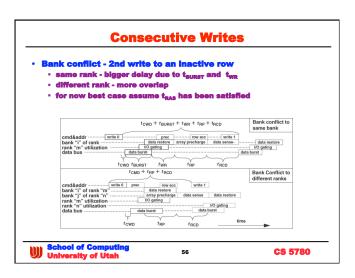

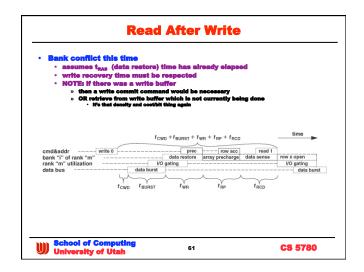

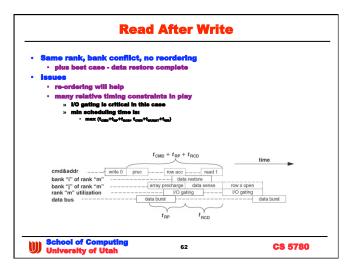

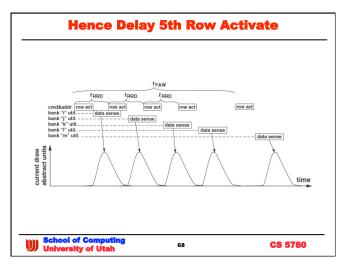

## Pipolining possible if requests are to open banks Itiming control is primarily restricted by burst length In one withing parameter for this one - phew! Ifferent banks allows tighter packing I show no new row needs to be prechaped a data restore time in overlapped I cas + faurar + fattras + fown | condaaddr | case can have a lot of variance in different DRAM technologies | cas + faurar + fattras + fown | fown |

### **Concluding Remarks Whiriwind Introduction** point is that there are a lot of tricking timing constraints that have to be understood to achieve maximum DRAM throughput Fortunately · for microcontroller interfaces » It's usually possible to abstract most of the hair away » since you usually just want to use a DRAM chip as a way to store a lot of data · high locality · simplified co and structure if you treat it much like an SRAM · so most of this hair can be ignored » slow microcontroller → slow access rate · for reference » typical DRAM datasheet from Micron is on the class web site School of Computing University of Utah CS 5780 72