| Cu                                                                      | rrent Plan          |                       |

|-------------------------------------------------------------------------|---------------------|-----------------------|

| • Today                                                                 |                     |                       |

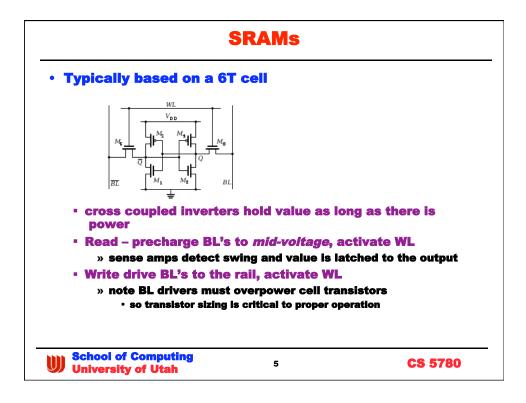

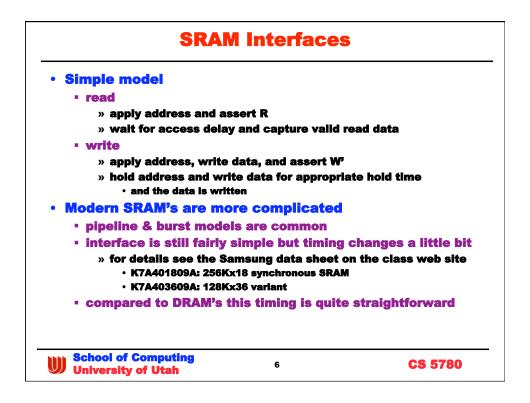

| <ul> <li>brief intro to SRAM</li> </ul>                                 |                     |                       |

| <ul> <li>more details on DRAM</li> </ul>                                |                     |                       |

| • Next Tuesday                                                          |                     |                       |

| • broad view of the NVR                                                 | AM playing field    |                       |

| <ul> <li>» as it looks today</li> <li>• note that things are</li> </ul> | changing rapidly    |                       |

| Next Thursday                                                           |                     |                       |

| <ul> <li>survey of cool gizmo's</li> </ul>                              | i                   |                       |

| » sensors, actuators, e                                                 | etc.                |                       |

| » namely things you m<br>microcontroller                                | ay want to use to a | surround your         |

| • Finish with midterm an                                                | d 6780 project      | demo's                |

| <ul> <li>demo's will be in the a</li> </ul>                             | ppropriate Wed      | & Friday lab sessions |

| » 5780 students in that<br>• of course all are we                       |                     | •                     |

| School of Computing<br>University of Utah                               | 4                   | <b>CS 5780</b>        |

| DR                                                                                                                                     | AM Evolutio           | n                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------|

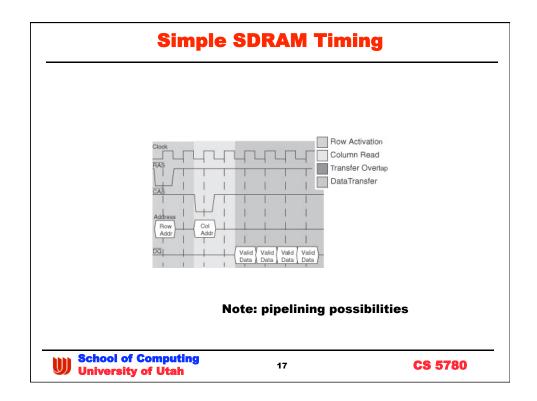

| <ul> <li>» Asynch DRAM - ac         <ul> <li>still clocked but</li> <li>» Fast Page Mode                 <ul></ul></li></ul></li></ul> | AM as a really slow S | RAM<br>he command lines<br>w buffer<br>ys valid<br>width sized nibbles<br>on now<br>s well |

| School of Computing                                                                                                                    | 16                    | CS 5780                                                                                    |

| DRAM chip<br>type    | DIMM Stick<br>Type   | Bus Clock<br>Rate<br>(MHz) | Memory<br>Clock<br>Rate<br>(MHz) | Channel<br>Bandwidth<br>(GB/s) | non-ECC<br>Channel<br>Width | ECC<br>Channel<br>Width | Prefetch<br>Buffer<br>Width | Vdd        | Read<br>Latency<br>Typical<br>(bus<br>cycles) | DIMM<br>pins |

|----------------------|----------------------|----------------------------|----------------------------------|--------------------------------|-----------------------------|-------------------------|-----------------------------|------------|-----------------------------------------------|--------------|

| DDR-200              | PC-1600              | 100                        | 100                              | 1.6                            | 64                          | 72                      | 2                           | 2.5        | 2-3                                           | 184          |

| DDR-266              | PC-2100              | 133                        | 133                              | 2.133                          | 64                          | 72                      | 2                           | 2.5        | 2-3                                           | 184          |

| DDR-333              | PC-2700              | 167                        | 167                              | 2.667                          | 64                          | 72                      | 2                           | 2.5        | 2-3                                           | 184          |

| DDR-400              | PC3200               | 200                        | 200                              | 3.2                            | 64                          | 72                      | 2                           | 2.5        | 2-3                                           | 184          |

| DDR2-400             | PC2-3200             | 100                        | 200                              | 3.2                            | 64                          | 72                      | 4                           | 1.8        | 3-9                                           | 240          |

| DDR2-533             | PC2-4200             | 133                        | 266                              | 4.267                          | 64                          | 72                      | 4                           | 1.8        | 3-9                                           | 240          |

| DDR2-667<br>DDR2-800 | PC2-5300<br>PC2-6400 | 167<br>200                 | 333<br>400                       | 5.333<br>6.4                   | 64<br>64                    | 72<br>72                | 4                           | 1.8<br>1.8 | 3-9<br>3-9                                    | 240<br>240   |

| DDR2-000             | FC2-0400             | 200                        | 400                              | 0.4                            | 04                          | 12                      | 4                           | 1.0        | 3-9                                           | 240          |

| DDR3-800             | PC3-6400             | 100                        | 400                              | 6.4                            | 64                          | 72                      | 8                           | 1.5        | ?                                             | 240          |

| DDR3-1066            | PC3-8500             | 133                        | 533                              | 8.53                           | 64                          | 72                      | 8                           | 1.5        | ?                                             | 240          |

| DDR3-1333            | PC3-10600            | 167                        | 667                              | 10.67                          | 64                          | 72                      | 8                           | 1.5        | ?                                             | 240          |

| DDR3-1600            | PC3-17000            | 200                        | 1066                             | 18.06                          | 64                          | 72                      | 8                           | 1.5        | ?                                             | 240          |

|                      |                      |                            |                                  |                                |                             |                         |                             |            |                                               |              |

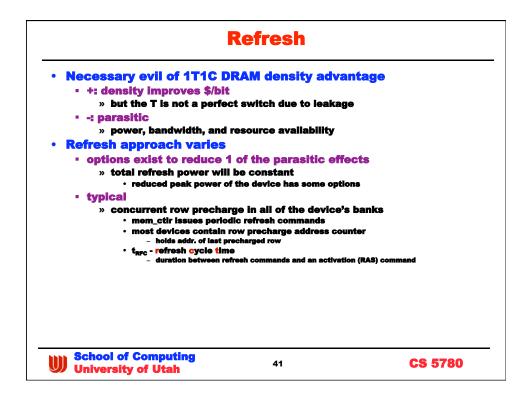

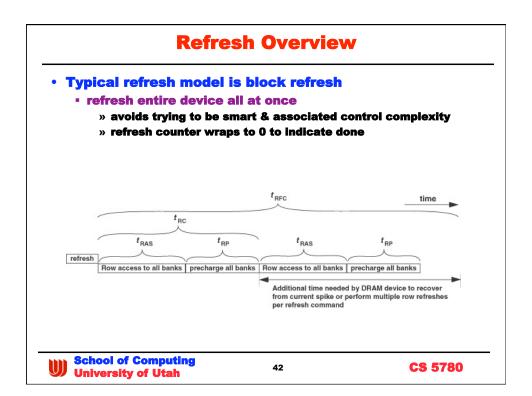

| • t <sub>RFC</sub> |                   | <mark>ng up</mark><br>es availa | bility =: | => elow    | or eveto  | m mom   | 0.77/              |                           |

|--------------------|-------------------|---------------------------------|-----------|------------|-----------|---------|--------------------|---------------------------|

|                    | ecreas<br>endor d |                                 | ibility - | -> 310W    | er syste  |         | Ul y               |                           |

| - •                |                   |                                 | - 64 me . | ofreeh m   | oried     |         |                    |                           |

|                    | -                 | inside the                      |           | -          |           |         |                    |                           |

|                    | • 6               | ven though                      | the nump  | er of row: | s goes up |         |                    |                           |

|                    |                   |                                 |           |            |           |         |                    |                           |

|                    |                   |                                 |           |            |           |         |                    |                           |

|                    |                   |                                 |           |            |           |         |                    |                           |

|                    |                   | Device                          |           |            | Row Size  | Refresh |                    |                           |

| Family             | Vdd               | Capacity<br>Mb                  | # Banks   | # Rows     | kow Size  | Count   | t <sub>ec</sub> ns | +                         |

| DDR                | 2.5V              | 256                             | 4 June    | 8192       | 1         | 8192    | 60                 | t <sub>RFC</sub> ns<br>67 |

| DDK                | 2.50              | 512                             | 4         | 8192       | 2         | 8192    | 55                 | 70                        |

| DDR2               | 1.8V              | 256                             | 4         | 8192       | 1         | 8192    | 55                 | 75                        |

| DURZ               | 1.04              | 512                             | 4         | 16384      | 1         | 8192    | 55                 | 105                       |

|                    |                   | 1024                            | 8         | 16384      | 1         | 8192    | 54                 | 127.5                     |

|                    |                   | 2048                            | 8         | 32768      | 1         | 8192    | ~                  | 197.5                     |

|                    |                   | 4096                            | 8         | 65536      | 1         | 8192    | ~                  | 327.5                     |

|                    |                   |                                 | -         |            | _         |         |                    |                           |

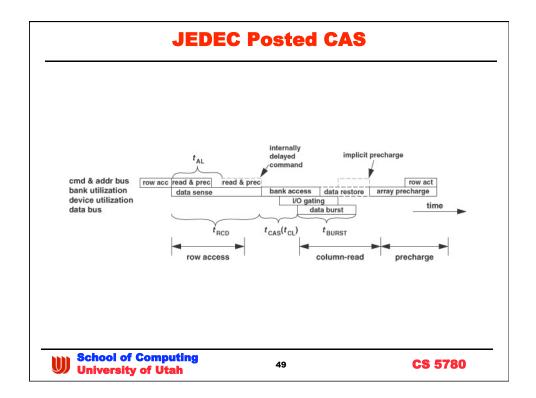

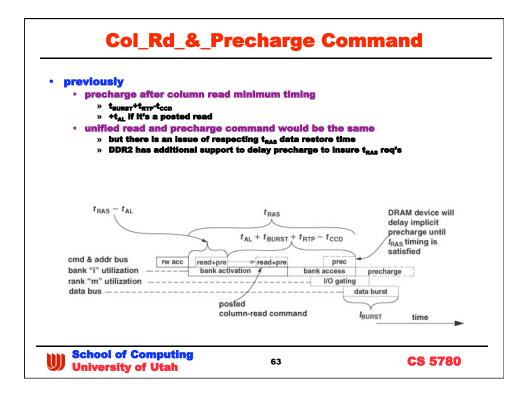

| <ul> <li>t<sub>RAS</sub> lockout <ul> <li>internal timer to make sure t<sub>RAS</sub> isn<sup>3</sup>t violated</li> <li>if col_rd_pch issues before data restore complete <ul> <li>device delays the implicit precharge command</li> </ul> </li> <li>allows closed page systems to issue col_rd_pch w/ optimistic til <ul> <li>mem_ctir doesn't need to worry about precharge of random row acces</li> </ul> </li> <li>Posted CAS <ul> <li>CAS issued but delayed (posted) by t<sub>AL</sub> cycles</li> <li>t<sub>AL</sub> - added latency to column access <ul> <li>programmed into the device</li> <li>usually once via initialization commands</li> </ul> </li> <li>XDR does same thing via CAS tag <ul> <li>logs of mem_ctir flexibility and complexity hides in this one</li> <li>1 simplification</li> <li>MC can issue posted CAS immediately after read</li> <li>t<sub>AL</sub> is set to respect the other timing constraints once</li> </ul> </li> </ul></li></ul></li></ul> | <b>Other DDR2 Trends</b>                                                       |         |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------|--|--|--|--|--|

| <ul> <li>» If col_rd_pch issues before data restore complete         <ul> <li>device delays the implicit precharge command</li> <li>allows closed page systems to issue col_rd_pch w/ optimistic til             <ul></ul></li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RAS lockout                                                                    |         |  |  |  |  |  |

| <ul> <li>device delays the implicit precharge command</li> <li>allows closed page systems to issue col_rd_pch w/ optimistic ti         <ul> <li>mem_ctir doesn't need to worry about precharge of random row acces</li> </ul> </li> <li>Posted CAS         <ul> <li>CAS issued but delayed (posted) by t<sub>AL</sub> cycles</li> <li>t<sub>AL</sub> - added latency to column access</li> <li>programmed into the device</li> <li>usually once via initialization commands</li> </ul> </li> <li>XDR does same thing via CAS tag         <ul> <li>logs of mem_ctir flexibility and complexity hides in this one</li> <li>1 simplification</li> <li>MC can issue posted CAS immediately after read</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                 | <ul> <li>internal timer to make sure t<sub>RAS</sub> isn't violated</li> </ul> |         |  |  |  |  |  |

| <ul> <li>mem_ctir doesn't need to worry about precharge of random row acces</li> <li>Posted CAS</li> <li>CAS issued but delayed (posted) by t<sub>AL</sub> cycles</li> <li>» t<sub>AL</sub> - added latency to column access</li> <li>» programmed into the device</li> <li>usually once via initialization commands</li> <li>XDR does same thing via CAS tag</li> <li>» logs of mem_ctir flexibility and complexity hides in this one</li> <li>» 1 simplification</li> <li>MC can issue posted CAS immediately after read</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                |         |  |  |  |  |  |

| <ul> <li>CAS issued but delayed (posted) by t<sub>AL</sub> cycles         <ul> <li>t<sub>AL</sub> - added latency to column access</li> <li>programmed into the device</li> <li>usually once via initialization commands</li> </ul> </li> <li>XDR does same thing via CAS tag         <ul> <li>logs of mem_ctir flexibility and complexity hides in this one</li> <li>1 simplification             <ul> <li>MC can issue posted CAS immediately after read</li> </ul> </li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                | •       |  |  |  |  |  |

| <ul> <li>* t<sub>AL</sub> - added latency to column access         <ul> <li>programmed into the device</li> <li>usually once via initialization commands</li> </ul> </li> <li>* XDR does same thing via CAS tag         <ul> <li>logs of mem_ctir flexibility and complexity hides in this one</li> <li>* 1 simplification             <ul> <li>MC can issue posted CAS immediately after read</li> </ul> </li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | osted CAS                                                                      |         |  |  |  |  |  |

| <ul> <li>programmed into the device</li> <li>usually once via initialization commands</li> <li>XDR does same thing via CAS tag</li> <li>» logs of mem_ctir flexibility and complexity hides in this one</li> <li>» 1 simplification</li> <li>• MC can issue posted CAS immediately after read</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>CAS issued but delayed (posted) by t<sub>AL</sub> cycles</li> </ul>   |         |  |  |  |  |  |

| <ul> <li>usually once via initialization commands</li> <li>XDR does same thing via CAS tag         <ul> <li>logs of mem_ctir flexibility and complexity hides in this one</li> <li>1 simplification             <ul> <li>MC can issue posted CAS immediately after read</li> </ul> </li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | » t <sub>AL</sub> - added latency to column access                             |         |  |  |  |  |  |

| <ul> <li>XDR does same thing via CAS tag         <ul> <li>logs of mem_ctir flexibility and complexity hides in this one</li> <li>1 simplification                 <ul> <li>MC can issue posted CAS immediately after read</li> </ul> </li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • • • • • • • • • • • • • • • • • • •                                          |         |  |  |  |  |  |

| <ul> <li>» logs of mem_ctir flexibility and complexity hides in this one</li> <li>» 1 simplification</li> <li>• MC can issue posted CAS immediately after read</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | · · · · · · · · · · · · · · · · · · ·                                          |         |  |  |  |  |  |

| <ul> <li>» 1 simplification</li> <li>• MC can issue posted CAS immediately after read</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                |         |  |  |  |  |  |

| MC can issue posted CAS immediately after read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • - • • • •                                                                    | s one   |  |  |  |  |  |

| • $\mathbf{t}_{AL}$ is set to respect the other timing constraints once                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                |         |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                |         |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                |         |  |  |  |  |  |

| School of Computing<br>University of Utah 48 CS 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                | CS 5780 |  |  |  |  |  |

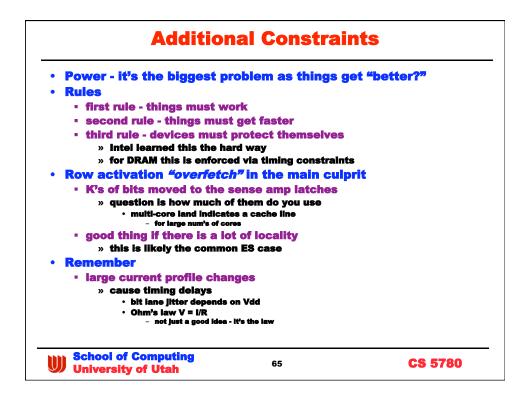

| <b>Double Edged Sword</b>                                                                                   |                                                 |                                         |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------|--|--|--|--|--|

| Active power                                                                                                |                                                 |                                         |  |  |  |  |  |

| • P <sub>a</sub> = aCV <sup>2</sup> f                                                                       |                                                 |                                         |  |  |  |  |  |

| <ul> <li>non-adiabatic chargine re</li> </ul>                                                               | egime                                           |                                         |  |  |  |  |  |

| <ul> <li>~.5P given off as heat</li> </ul>                                                                  |                                                 |                                         |  |  |  |  |  |

| » the other half is returned                                                                                | ed to the power supply                          |                                         |  |  |  |  |  |

| <ul> <li>Vdd variations on the p</li> <li>also supply tolerance</li> <li>requires over provision</li> </ul> | to high variance loads is a                     |                                         |  |  |  |  |  |

| <ul> <li>higher temps increase particular</li> </ul>                                                        | assive P component                              | t i i i i i i i i i i i i i i i i i i i |  |  |  |  |  |

| <ul> <li>Faster is better</li> </ul>                                                                        |                                                 |                                         |  |  |  |  |  |

| <ul> <li>except for power since t</li> </ul>                                                                | ooth f and a go up                              |                                         |  |  |  |  |  |

| » hence so does P and le                                                                                    | akage                                           |                                         |  |  |  |  |  |

| leakage impacts resou     const impacts resou                                                               | urce availability<br>nd the 64 ms standard targ | -                                       |  |  |  |  |  |

| · can't ignore renesn an                                                                                    | iu the 04 ms standard targ                      | e.                                      |  |  |  |  |  |

|                                                                                                             |                                                 |                                         |  |  |  |  |  |

|                                                                                                             |                                                 |                                         |  |  |  |  |  |

|                                                                                                             |                                                 |                                         |  |  |  |  |  |

|                                                                                                             |                                                 |                                         |  |  |  |  |  |

| School of Computing                                                                                         | 66                                              | <b>CS 5780</b>                          |  |  |  |  |  |

| University of Utah                                                                                          |                                                 | 03 5700                                 |  |  |  |  |  |

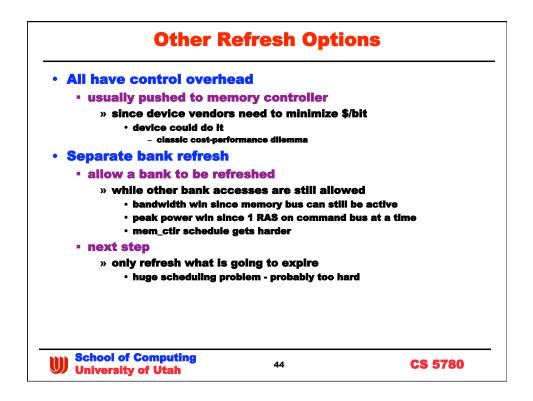

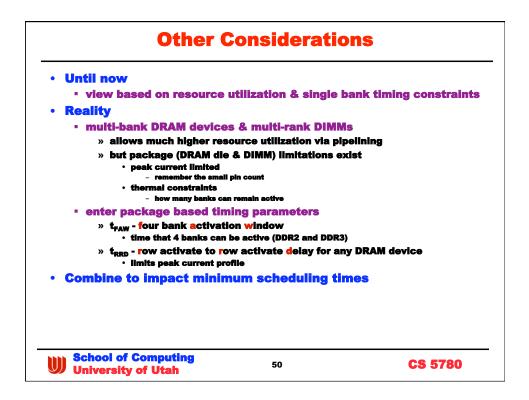

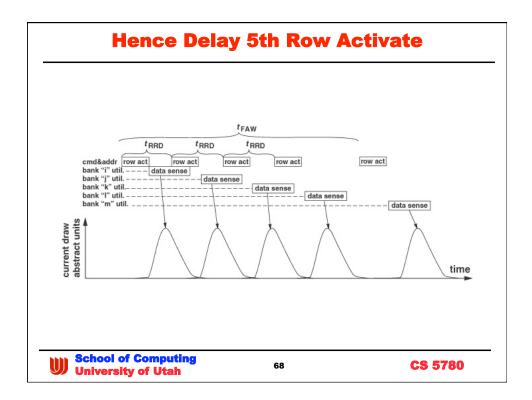

| # of<br>• • | it row activation - t <sub>RRD</sub><br>active banks<br>conflict between perform<br>current limit is 4 bank act<br>n get worse as device | tivation window | w t <sub>FAW</sub> |            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|------------|

|             |                                                                                                                                          | Micron          |                    |            |

|             | <b>Device Configuration</b>                                                                                                              |                 | 56 Mb x 8 12       | 28 Mb x 16 |

|             | Bus width                                                                                                                                | 4               | 8                  | 16         |

|             | Bank count                                                                                                                               | 8               | 8                  | 8          |

|             | Row Count                                                                                                                                | 16384           | 16384              | 8196       |

|             | Column Count                                                                                                                             | 2048            | 1024               | 1024       |

|             |                                                                                                                                          | 8192            | 8192               | 16384      |

|             | Row Size                                                                                                                                 |                 | 7.5                | 10         |

|             | Row Size<br>tRRD ns                                                                                                                      | 7.5             | 710                |            |

|             |                                                                                                                                          | 7.5<br>37.5     | 37.5               | 50         |

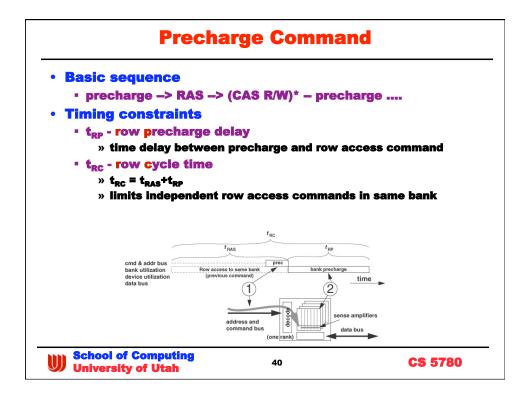

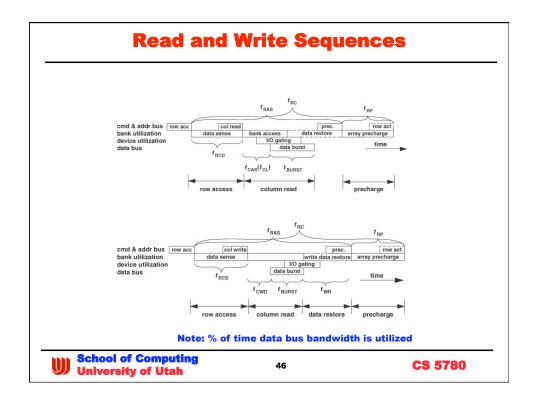

| Parameter | Description                                              | ٦ |

|-----------|----------------------------------------------------------|---|

| tAL       | added latency to column accesses for posted CAS          | - |

| tBURST    | data burst duration on the data bus                      | 1 |

| tCAS      | interval between CAS and start of data return            | 1 |

|           | column command delay - determined by internal burst      | 1 |

| tCCD      | timing                                                   |   |

| tCMD      | time command is on bus from MC to device                 | 1 |

|           | column write delay, CAS write to write data on the bus   | 7 |

| tCWD      | from the MC                                              |   |

|           | rolling temporal window for how long four banks can      | 7 |

| tFAW      | remain active                                            |   |

| tOST      | interval to switch ODT control from rank to rank         |   |

| tRAS      | row access command to data restore interval              |   |

|           | interval between accesses to different rows in same bank |   |

| tRC       | = tRAS+tRP                                               |   |

| tRCD      | interval between row access and data ready at sense amps | : |

| tRFC      | interval between refresh and activation commands         |   |

|           | interval for DRAM array to be precharged for another row |   |

| tRP       | access                                                   |   |

|           | interval between two row activation commands to same     |   |

| tRRD      | DRAM device                                              | _ |

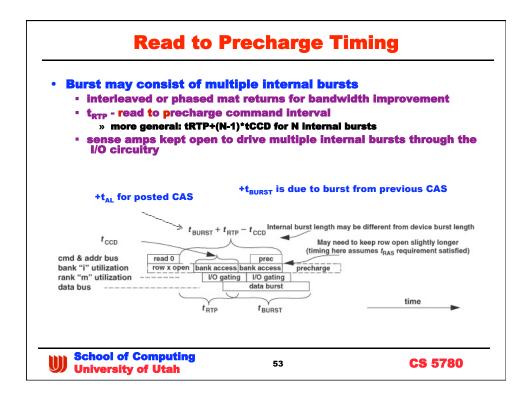

| tRTP      | interval between a read and a precharge command          | _ |

| tRTRS     | rank to rank switching time                              | _ |

|           | write recovery time - interval between end of write data |   |

| tWR       | burst and a precharge command                            | _ |

|           | interval between end of write data burst and start of a  |   |

| tWTR      | column read command                                      |   |

## **Summary Minimal Timing Equations**

| University of Co |      |        |        |        | -                             | 71                                | CS 5780 |

|------------------|------|--------|--------|--------|-------------------------------|-----------------------------------|---------|

|                  | P    | F      | s      | а      | TRFC                          |                                   |         |

|                  | F    | F      | s      | а      | tRFC<br>tRFC                  |                                   |         |

|                  | w    | Р      | s      | s      | +<br>tBURST+tW<br>R           | tBURST prev CASW same rank        |         |

| rank column      | R    | Ρ      | s      | s      | tCCD<br>tAL+tCWD              | tBURST of previous CAS, same rank |         |

| chip – ignore    | A    | Р      | s      | s      | tRAS<br>tAL+tBURS<br>T+ tRTP- |                                   |         |

| For single DRAM  | w    | w      | d      | а      | ST                            | tBURST prev CASW diff rank        |         |

|                  | w    | w      | s      | а      | T, tCCD)<br>tBURST+tO         | tBURST prev CASW same rank        |         |

| care about       | R    | w      | а      | а      | tCWD<br>Max(tBURS             | tBURST prev. CAS any rank         |         |

| you really       | -    |        |        |        | ST+tRTRS-                     |                                   |         |

| This is what     | А    | vv     | 5      | 5      | tCAS+tBUR                     |                                   |         |

|                  | W    | R<br>W | d<br>s | a<br>s | tCAS<br>tRCD-tAL              | tBURST prev CASW diff rank        |         |

|                  |      |        |        |        | tCWD+tBU<br>RST+tRTRS         |                                   |         |

|                  | w    | R      | s      | а      | tWTR                          | tBURST prev CASW same rank        |         |

| a=any            |      |        |        |        | tBURST+                       |                                   |         |

| d=different      | R    | R      | d      | а      | tRTRS<br>tCWD+                | tBURST prev. CAS diff. rank       |         |

| s=same           |      |        |        | -      | tBURST+                       |                                   |         |

| F=Refresh        | R    | R      | s      | а      | Max(tBURS<br>T, tCCD)         | tBURST of previous CAS, same rank |         |

| P=precharge      | Α    | R      | s      | s      | tRCD-tAL                      | tAL=0 unless posted CAS           |         |

|                  | F    | A      | s      | s      | tRFC                          |                                   |         |

| W=col wr         | P    | A      | s      | d      | tRP                           | plus traw for 5th RAS same rank   |         |

| R=col rd         | A    | A      | s<br>s | s<br>d | tRC<br>tRRD                   | plus tFAW for 5th RAS same rank   |         |

| A=row access     | Prev |        |        |        | Min. Timing                   | Notes                             |         |

| Conclu                                                                              | uding Rema                            | rks                    |

|-------------------------------------------------------------------------------------|---------------------------------------|------------------------|

| • Whirlwind introduction                                                            | n                                     |                        |

| <ul> <li>point is that there are<br/>that have to be unde<br/>throughput</li> </ul> |                                       |                        |

| • Fortunately                                                                       |                                       |                        |

| for microcontroller in                                                              | terfaces                              |                        |

| » it's usually possible                                                             | to abstract most of                   | the hair away          |

| » since you usually ju<br>store a lot of data<br>• high locality                    | st want to use a DR                   | AM chip as a way to    |

| • •                                                                                 | nd structure if you treat             | t it much like an SRAM |

| <ul> <li>so most of this hair c</li> </ul>                                          |                                       |                        |

| » slow microcontrolle                                                               | · · · · · · · · · · · · · · · · · · · | e                      |

| • for reference                                                                     |                                       |                        |

| » typical DRAM datas                                                                | heet from Micron is                   | on the class web site  |

|                                                                                     |                                       |                        |

| School of Computing                                                                 |                                       |                        |