| TRANSMIT     | Set n=7                                                                     | Bit counter |

|--------------|-----------------------------------------------------------------------------|-------------|

| TLOOP        | On fall of Sck, set Data=bn<br>Set n=n-1<br>Goto TLOOP if n>=0              | Output bit  |

|              | Set Data=1                                                                  | Idle output |

|              | Set n=7                                                                     | Bit counter |

| RLOOP        | On rise of Sck, read data<br>Set bn=Data<br>Set n=n-1<br>Goto RLOOP if n>=0 | Input bit   |

|              |                                                                             |             |

| School of Co | omputing 6                                                                  | CS 578      |

| MODFEN        | SSOE | Master N                                                         | /lode (MSTI  | R=1) Slave M  | lode (MSTR=0) |

|---------------|------|------------------------------------------------------------------|--------------|---------------|---------------|

| 0             | 0    | PM3 not                                                          | used with SP | I PM3 is      | SS input      |

| 0             | 1    | PM3 not                                                          | used with SP | I PM3 is      | SS input      |

| 1             | 0    | PM3 is $\overline{SS}$ input w/MODF PM3 is $\overline{SS}$ input |              |               | SS input      |

| 1             | 1    | PM3 is 5                                                         | S output     | PM3 is        | 55 input      |

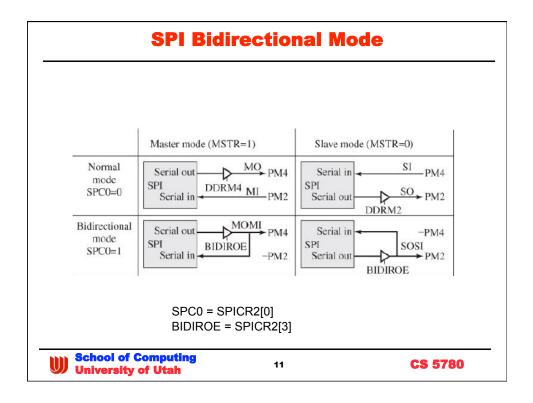

| Pin Mode      | MSTR | SPC0                                                             | BIDIROE      | MISO          | MOSI          |

| Normal        | 1    | 0                                                                | Х            | Master In     | Master Out    |

| Bidirectional | 1    | 1                                                                | 0            | MISO not used | Master In     |

|               |      |                                                                  | 1            |               | Master I/O    |

| Normal        | 0    | 0                                                                | Х            | Slave Out     | Slave In      |

| Bidirectional | 0    | 1                                                                | 0            | Slave In      | MOSI not used |

|               |      |                                                                  | 1            | Slave I/O     |               |

|               |      |                                                                  |              |               |               |

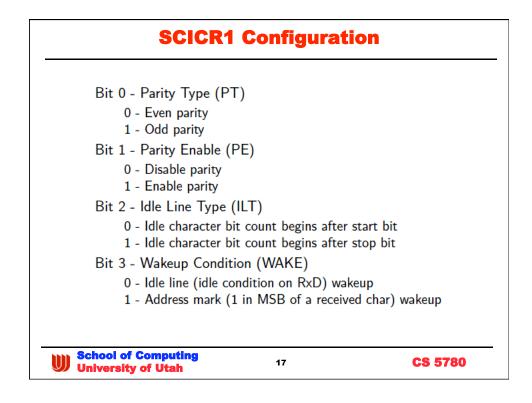

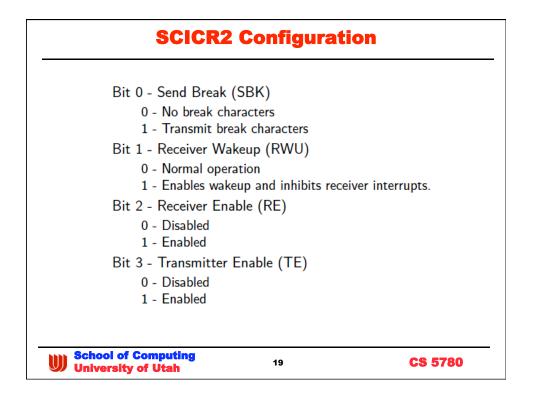

| В | it 4 - Data Format (M                                                   | 1)                                           |                                         |

|---|-------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------|

| 2 | 0 - 1 start bit, 8 dat                                                  | ,                                            |                                         |

|   | 1 - 1 start bit, 9 dat                                                  |                                              |                                         |

| В | it 5 - Receiver Source                                                  | (RSRC)                                       |                                         |

|   |                                                                         | to transmitter conne<br>to transmitter conne |                                         |

| В | it 6 - SCI Stop in Wai<br>0 - SCI enabled in w<br>1 - SCI disabled in w | ait mode                                     |                                         |

| В | it 7 - Loop Select (LO                                                  | OPS)                                         |                                         |

|   |                                                                         |                                              | is disconnected from<br>used for GPIO.) |

|   | chool of Computing<br>niversity of Utah                                 | 18                                           | CS 5780                                 |

| More SCI                                                                                                           | CR2 Configu           | ration               |

|--------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|

| Bit 4 - Idle Line Inte                                                                                             | errupt Enable (ILIE)  |                      |

| 0 - IDLE interru                                                                                                   | pts disabled          |                      |

| 1 - IDLE interru                                                                                                   | pts enabled           |                      |

| Bit 5 - Receiver Full                                                                                              | Interrupt Enable (F   | RIE)                 |

| 0 - RDRF and C                                                                                                     | R interrupts disabled |                      |

| 1 - RDRF and C                                                                                                     | R interrupts enabled  |                      |

| Bit 6 - Transmission                                                                                               | Complete Interrupt    | Enable (TCIE)        |

| 0 - TC interrupt                                                                                                   | s disabled            |                      |

| 1 - TC interrupt                                                                                                   | s enabled             |                      |

| Bit 7 - Transmitter                                                                                                | Interrupt Enable (TI  | E)                   |

| 0 - TDRE interr                                                                                                    | upts disabled         | ,                    |

| 1 - TDRE intern                                                                                                    | upts enabled          |                      |

| OR signals overrun (next byte read)<br>the SCDR is already full – buffer ov<br>RDRF – signals receive data registe | errun)                | x shift register but |

| School of Computing<br>University of Utah                                                                          | 20                    | <b>CS 5780</b>       |

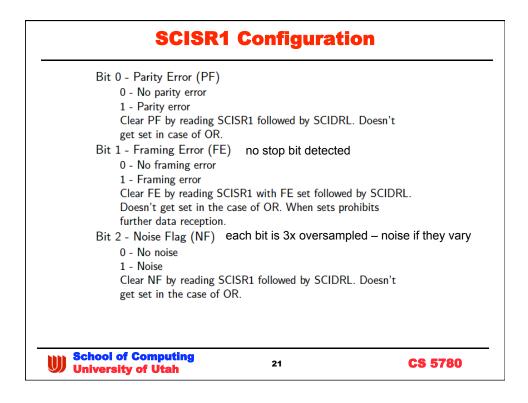

| More SCI                                  | SR1 Config                                          | uration             |

|-------------------------------------------|-----------------------------------------------------|---------------------|

| Bit 3 - Overrun (OR)                      |                                                     |                     |

| 0 - No overrun                            |                                                     |                     |

| 1 - Overrun                               |                                                     |                     |

| 0                                         | ost, but the current dat<br>ISR1 with OR set follov |                     |

| Bit 4 - Idle Line (IDLE                   | E)                                                  |                     |

| 0 - Receiver input<br>last IDLE flag clea | is active or has never b<br>r                       | ecome active since  |

| 1 - Receiver input                        |                                                     |                     |

| Clear IDLE flag by<br>SCIDRL.             | reading SCISR1 with I                               | DLE set followed by |

| Bit 5 - Receive Data F                    | Register Full (RDRF)                                |                     |

| 0 - Data not availa                       | able in SCI data registe                            | r                   |

| 1 - Received data                         | available in SCI data re                            | egister             |

| Clear RDRF by rea<br>SCIDRL.              | ading SCISR1 with RDI                               | RF set followed by  |

| School of Computing                       | 22                                                  | CS 5780             |