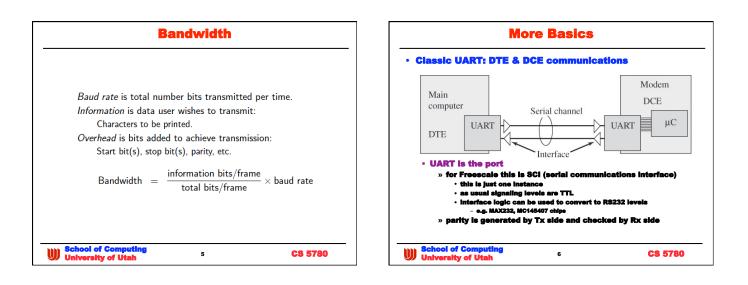

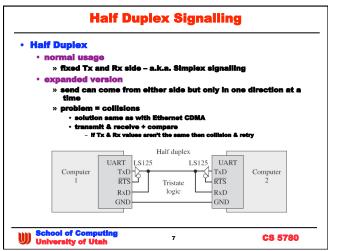

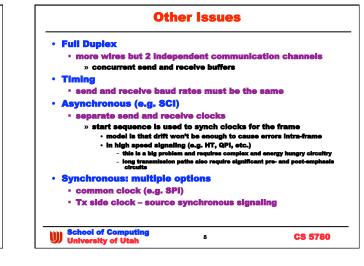

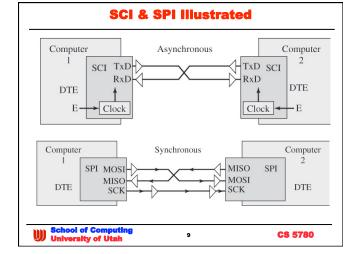

**Introduction to Serial I/O**

| Pin | Signal | Description         | True | DTE | DCE |

|-----|--------|---------------------|------|-----|-----|

| 1   | DCD    | Data Carrier Detect | +12  | In  | Out |

| 2   | RxD    | Receive Data        | -12  | In  | Out |

| 3   | TxD    | Transmit Data       | -12  | Out | In  |

| 4   | DTR    | Data Terminal Rdy   | +12  | Out | In  |

| 5   | SG     | Signal Ground       |      |     |     |

| 6   | DSR    | Data Set Ready      | +12  | In  | Out |

| 7   | RTS    | Request to Send     | +12  | Out | In  |

| 8   | CTS    | Clear to Send       | +12  | In  | Out |

| 9   | RI     | Ring Indicator      | +12  | In  | Out |

| Specification           | RS232D                 | RS423A                          | RS422     | RS485   |

|-------------------------|------------------------|---------------------------------|-----------|---------|

| Mode of operation       | Single-ended           | Single-ended                    | Diff.     | Diff.   |

| Drivers on one line     | 1                      | 1                               | 1         | 32      |

| Receivers on one line   | 1                      | 10                              | 10        | 32      |

| Max distance (ft)       | 50                     | 4,000                           | 4,000     | 4,000   |

| Max data rate           | 20kb/s                 | 100kb/s                         | 10Mb/s    | 10Mb/s  |

| Max driver output       | $\pm 25V$              | ±6V                             | -0.25/+6V | -7/+12V |

| Receiver input          | $\pm 15V$              | $\pm 12V$                       | $\pm 7V$  | -7/+12V |

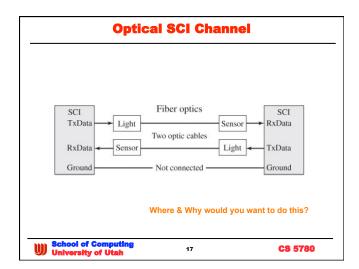

| SCI<br>TxData<br>RxData | 301 A<br>B<br>A'<br>B' | A' SP:<br>A' B'<br>A<br>B'<br>A |           | Data    |

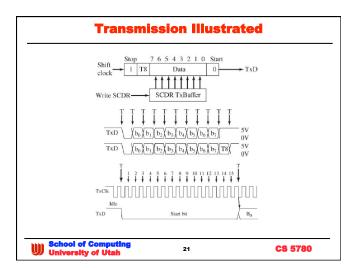

| Pseudo Cod | e for | Transmi | ission | Process |

|------------|-------|---------|--------|---------|

|------------|-------|---------|--------|---------|

| TRANSMIT                         | Set TxD=0     |       | Output start bit  |

|----------------------------------|---------------|-------|-------------------|

|                                  | Wait 16 clock | times | Wait 1 bit time   |

|                                  | Set n=0       |       | Bit counter       |

| TLOOP                            | Set TxD=bn    |       | Output data bit   |

|                                  | Wait 16 clock | times | Wait 1 bit time   |

|                                  | Set n=n+1     |       |                   |

|                                  | Goto TLOOP if | n<=7  |                   |

|                                  | Set TxD=T8    |       | Output T8 bit     |

|                                  | Wait 16 clock | times | Wait 1 bit time   |

|                                  | Set TxD=1     |       | Output a stop bit |

|                                  | Wait 16 clock | times | Wait 1 bit time   |

|                                  |               |       |                   |

|                                  |               |       |                   |

| School of Com<br>University of U |               | 22    | <b>CS 5780</b>    |

## **Status Bits Generated by the Receiver**

Receive Data Register Full flag (RDRF), set when new data available, clear by reading RDRF and SCDR. Receiver Idle flag (IDLE), set when receiver line is idle, clear by reading IDLE, then reading SCDR. Overrun flag (OR), set when input data lost because previous frame not read, clear by reading OR and SCDR. Noise flag (NF), set when input is noisy, clear by reading NF flag, then reading SCDR. Framing error (FE), set when stop bit is incorrect, clear by reading FE, then reading SCDR. 25

School of Computing University of Utah

CS 5780

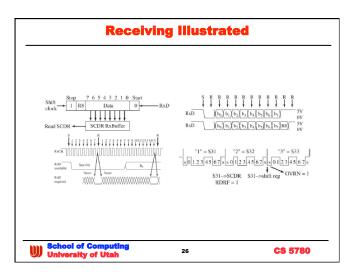

| RECEIVE                 | Goto RECEIVE if RxD=1            | Wait for start bit   |

|-------------------------|----------------------------------|----------------------|

|                         | Wait 8 clock times               | Wait half a bit time |

|                         | Goto RECEIVE if RxD=1<br>Set n=0 | False start?         |

| RLOOP                   | Wait 16 clock times              | Wait 1 bit time      |

|                         | Set bn=RxD                       | Input data bit       |

|                         | Set n=n+1                        |                      |

|                         | Goto RLOOP if n<=7               |                      |

|                         | Wait 16 clock times              | Wait 1 bit time      |

|                         | Set R8=RxD                       | Read R8 bit          |

|                         | Wait 16 clock times              | Wait 1 bit time      |

|                         | Set FE=1 if RxD=0                | Framing error if     |

|                         |                                  | no stop bit          |

|                         | Hare to ereen ermoo              | Framing error if     |

| chool of (<br>niversity | Computing 27                     | CS 5780              |

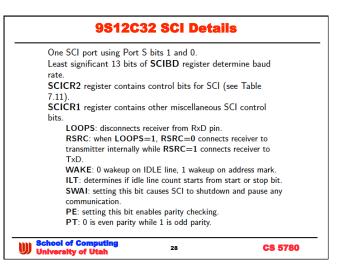

## **More SCI Details**

Flags in SCISR1 register can be read but not modified by software. The error conditions are also reported in the SCISR1 register including parity flag, PF, set on parity errors. The SCISR2 register contains two mode control and one status bit.  $\ensuremath{\mathsf{BRK13}}\xspace$  break character is 13 or 14 bits when 1 and 10 or 11 bits when 0. TXDIR: specifies direction of the TxD pin in single-wire mode. RAF: 1 when frame is being received. The SCIDRL register contains data transmitted and received. The SCIDRH register contains the 9th data bits. School of Computing University of Utah 29 CS 5780

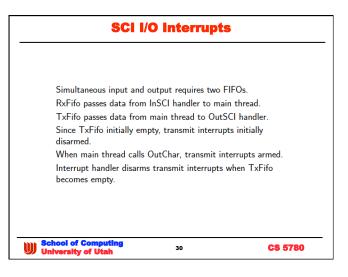

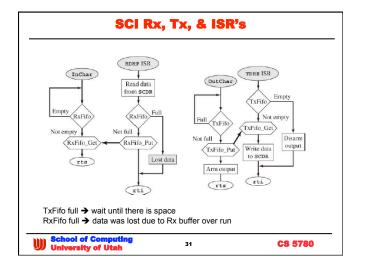

| SCI Interface ISR                                 |         |

|---------------------------------------------------|---------|

| // RDRF set on new receive data                   |         |

| <pre>// TDRE set on empty transmit register</pre> |         |

| <pre>interrupt 20 void SciHandler(void){</pre>    |         |

| char data;                                        |         |

| if(SCISR1 & RDRF){                                |         |

| <pre>RxFifo_Put(SCIDRL); // clears RDRF</pre>     |         |

| }                                                 |         |

| if((SCICR2&TIE)&&(SCISR1&TDRE)){                  |         |

| if(TxFifo_Get(&data)){                            |         |

| SCIDRL = data; // clears TDRE                     |         |

| }                                                 |         |

| else{                                             |         |

| SCICR2 = 0x2c; // disarm TDRE                     |         |

| }                                                 |         |

| }                                                 |         |

| }                                                 |         |

|                                                   |         |

|                                                   |         |

| School of Computing<br>University of Utah 33      | CS 5780 |

| SCI In/Out Character                               |         |

|----------------------------------------------------|---------|

| // Input ASCII character from SCI                  |         |

| // spin if RxFifo is empty                         |         |

| <pre>char SCI_InChar(void){ char letter;</pre>     |         |

| <pre>while (RxFifo_Get(&amp;letter) == 0){};</pre> |         |

| return(letter);                                    |         |

| }                                                  |         |

| <pre>// Output ASCII character to SCI</pre>        |         |

| <pre>// spin if TxFifo is full</pre>               |         |

| <pre>void SCI_OutChar(char data){</pre>            |         |

| <pre>while (TxFifo_Put(data) == 0){};</pre>        |         |

| SCICR2 = 0xAC; // arm TDRE                         |         |

| }                                                  |         |

|                                                    |         |

|                                                    |         |

| School of Computing<br>University of Utah 34       | CS 5780 |

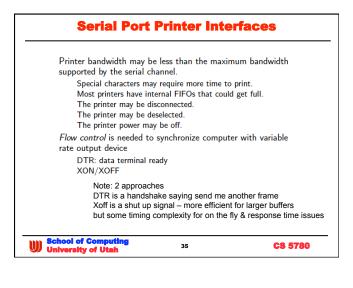

## Page 9

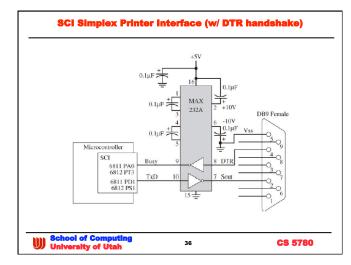

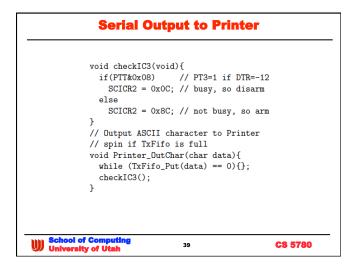

| <b>Seria</b> | l Out | tput | <b>w</b> / | DTR |

|--------------|-------|------|------------|-----|

|--------------|-------|------|------------|-----|

| DTI                                       | R Handshake ISR                                                                                                  |                |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------|

| void inte<br>TFLG1 =                      | aterrupt on any change of<br>wrrupt 11 IC3Han(void) {<br>= 0x08; // Ack, clear C3F<br>C3(); // Arm SCI if DTR=+1 |                |

|                                           |                                                                                                                  |                |

| School of Computing<br>University of Utah | 38                                                                                                               | <b>CS 5780</b> |

| JLI LZENNO CONE | SPI | <b>Pseudo</b> | Code |

|-----------------|-----|---------------|------|

|-----------------|-----|---------------|------|

| School of Co<br>University o |                                                                             | <b>CS 578</b> 0           |

|------------------------------|-----------------------------------------------------------------------------|---------------------------|

| RLOOP                        | On rise of Sck, read data<br>Set bn=Data<br>Set n=n-1<br>Goto RLOOP if n>=0 | Input bit                 |

| RECEIVE                      | Set n=7                                                                     | Bit counter               |

| ILUUP                        | Set Data=1<br>Set Data=1                                                    | Output bit<br>Idle output |

| TRANSMIT<br>TLOOP            | Set n=7<br>On fall of Sck, set Data=bn                                      | Bit counter               |

|      |       |                  |         | 3 = 3 | 55, PM5 = | = SCLK,    | PM4 = N      | NOSI,    |

|------|-------|------------------|---------|-------|-----------|------------|--------------|----------|

| an   | d Pl  | M2 =             | MISO.   |       |           |            |              |          |

| If ( | 6010  |                  | stor s  | -+ DI | DRM to r  | naka DM    |              | nd DM2   |

|      |       |                  | ster, s |       |           | ITAKE FIVE | 5, F 1014, a |          |

| ou   | tput  | s.               |         |       |           |            |              |          |

| Ca   | n he  | in ru            | n wai   | t or  | stop mod  | •          |              |          |

| Ca   | in De | : in Tu          | n, wai  | L, Or | 4 M       |            | 24 N         | /H-      |

| S    | PR2   | SPR1             | SPR0    | Div   | Freq      | Bit Time   | Freq         | Bit Time |

|      | 0     | 0                | 0       | 2     | 2 MHz     | 500 ns     | 12 MHz       | 83.3 ns  |

|      | 0     | 0                | 1       | 4     | 1 MHz     | 1 µs       | 6 MHz        | 166.7 ns |

|      | 0     | 1                | 0       | 8     | 500 kHz   | 2 µs       | 3 MHz        | 333.3 ns |

|      | 0     | 1                | 1       | 16    | 250 kHz   | 4 μs       | 1.5 MHz      |          |

|      | 1     | 0                | 0       | 32    | 125 MHz   | 8 µs       | 750 kHz      | 1.33 µs  |

|      | 1     | 0                | 1       | 64    | 62.5 kHz  | 16 µs      | 375 kHz      | 2.67 µs  |

|      | 1     | 1                | 0       | 128   | 31.25 kHz | 32 µs      | 187.5 kHz    | 5.33 µs  |

|      | 1     | 1                | 1       | 256   | 15.625kHz | 64 μs      | 93.75 kHz    | 10.67 μs |

|      |       |                  |         |       | SPIBR re  | egister    |              |          |

|      | 1     | 1                | 1       | 256   |           |            | 93.75 kHz    | 10.67 μs |

| Scho | o lo  | f Com<br>ty of U | puting  |       | 4         | 7          |              | CS 578   |

|                                 | Master mode (MSTR=1)                                     | Slave mode (MSTR=0)                       |

|---------------------------------|----------------------------------------------------------|-------------------------------------------|

| Normal<br>mode<br>SPC0=0        | Serial out<br>SPI<br>Scrial in<br>Scrial in<br>Scrial in | Serial in<br>SPI<br>Scrial out<br>DDRM2   |

| Bidirectional<br>mode<br>SPC0=1 | Serial out<br>SPI<br>Serial in<br>Serial in              | Serial in<br>SPI<br>Serial out<br>BIDIROE |

| MODFEN                    | SSOE | Master N | Aode (MSTI   | R=1) Slave M  | ode (MSTR=0)           |  |

|---------------------------|------|----------|--------------|---------------|------------------------|--|

| 0                         | 0    | PM3 not  | used with SP | I PM3 is S    | S input                |  |

| 0                         | 1    | PM3 not  | used with SP |               | PM3 is SS input        |  |

| 1                         | 0    | PM3 is 5 | 5 input w/M  |               | PM3 is <u>SS</u> input |  |

| 1                         | 1    | PM3 is 5 |              | PM3 is S      |                        |  |

|                           |      |          |              |               |                        |  |

| Pin Mode                  | MSTR | SPC0     | BIDIROE      | MISO          | MOSI                   |  |

| Normal                    | 1    | 0        | Х            | Master In     | Master Out             |  |

| Bidirectional             | 1    | 1        | 0            | MISO not used | Master In              |  |

|                           |      |          | 1            |               | Master I/O             |  |

| Normal                    | 0    | 0        | Х            | Slave Out     | Slave In               |  |

| Bidirectional             | 0    | 1        | 0            | Slave In      | MOSI not used          |  |

|                           |      |          | 1            | Slave I/O     |                        |  |

|                           |      |          |              |               |                        |  |

| School of C<br>University |      | ng       | 50           |               | CS 5780                |  |

| <b>Concluding Remarks</b>                                                |                   |                 |  |  |

|--------------------------------------------------------------------------|-------------------|-----------------|--|--|

| • Serial I/O is very comn                                                | non               |                 |  |  |

| <ul> <li>USB is obviously ever</li> </ul>                                | ywhere            |                 |  |  |

| <ul> <li>SPI &amp; SCI are more pr</li> </ul>                            | revalent in embed | ided systems    |  |  |

| » primarily because it                                                   |                   |                 |  |  |

| » most controllers sur                                                   |                   |                 |  |  |

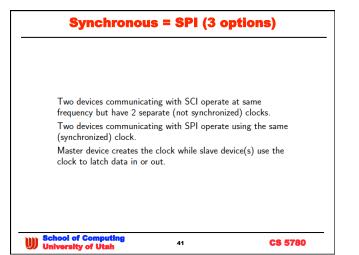

| <ul> <li>your kits support b</li> <li>a difference is synch t</li> </ul> |                   |                 |  |  |

| • Too much detail airea                                                  | •                 |                 |  |  |

| • but advise that you ta                                                 | · ·               | DAC application |  |  |

| <ul> <li>we'll go through the feature</li> </ul>                         |                   |                 |  |  |

| » in prep for Lab 8                                                      |                   |                 |  |  |

| • SPRING BREAK                                                           |                   |                 |  |  |

| <ul> <li>hope you have some f</li> </ul>                                 | fun               |                 |  |  |

| <ul> <li>hope I can catch up</li> </ul>                                  |                   |                 |  |  |

|                                                                          |                   |                 |  |  |

| School of Computing<br>University of Utah                                | 51                | CS 5780         |  |  |