| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ers<br>t be the same<br>s<br>clocks for the frame<br>h to cause errors intra-frame |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| <ul> <li>» concurrent send and receive buff</li> <li>Timing         <ul> <li>send and receive baud rates must</li> <li>Asynchronous (e.g. SCI)</li> <li>separate send and receive clock</li> <li>» start sequence is used to synch</li> <li>model is that drift won't be enouge</li> <li>in high speed signaling (e.g. HT, 0</li> <li>this is a big problem and requires</li> <li>long transmission paths also required</li> </ul> </li> <li>Synchronous: multiple options</li> </ul> | ers<br>t be the same<br>s<br>clocks for the frame<br>h to cause errors intra-frame |

| <ul> <li>Timing         <ul> <li>send and receive baud rates must</li> <li>Asynchronous (e.g. SCI)</li> <li>separate send and receive clock</li> <li>start sequence is used to synch</li> <li>model is that drift won't be enoug</li> <li>in high speed signaling (e.g. HT, 0</li> <li>this is a big problem and requires</li> <li>long transmission paths also required circuits</li> </ul> </li> <li>Synchronous: multiple options</li> </ul>                                       | t be the same<br>s<br>clocks for the frame<br>h to cause errors intra-frame        |

| <ul> <li>send and receive baud rates mustors</li> <li>Asynchronous (e.g. SCI)</li> <li>separate send and receive clock</li> <li>start sequence is used to synch</li> <li>model is that drift won't be enouged</li> <li>In high speed signaling (e.g. HT, Construction)</li> <li>this is a big problem and requires</li> <li>long transmission paths also required</li> <li>Synchronous: multiple options</li> </ul>                                                                   | s<br>clocks for the frame<br>h to cause errors intra-frame                         |

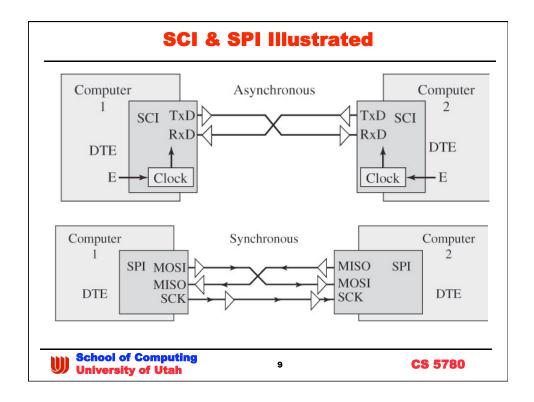

| <ul> <li>Asynchronous (e.g. SCI)</li> <li>separate send and receive clock</li> <li>» start sequence is used to synch</li> <li>• model is that drift won't be enoug</li> <li>• In high speed signaling (e.g. HT, C</li> <li>• this is a big problem and requires</li> <li>• long transmission paths also required</li> <li>• Synchronous: multiple options</li> </ul>                                                                                                                  | s<br>clocks for the frame<br>h to cause errors intra-frame                         |

| <ul> <li>separate send and receive clock</li> <li>» start sequence is used to synch</li> <li>• model is that drift won't be enoug</li> <li>• In high speed signaling (e.g. HT, e.g. this is a big problem and requires</li> <li>- long transmission paths also required circuits</li> <li>• Synchronous: multiple options</li> </ul>                                                                                                                                                  | locks for the frame<br>h to cause errors intra-frame                               |

| <ul> <li>start sequence is used to synch</li> <li>model is that drift won't be enough</li> <li>in high speed signaling (e.g. HT, or this is a big problem and requires</li> <li>this is a big problem and requires</li> <li>long transmission paths also requires</li> <li>Synchronous: multiple options</li> </ul>                                                                                                                                                                   | locks for the frame<br>h to cause errors intra-frame                               |

| <ul> <li>model is that drift won't be enoug</li> <li>in high speed signaling (e.g. HT, e.g. this is a big problem and requires         <ul> <li>this is a big problem and requires</li> <li>long transmission paths also required</li> </ul> </li> <li>Synchronous: multiple options</li> </ul>                                                                                                                                                                                       | h to cause errors intra-frame                                                      |

| <ul> <li>In high speed signaling (e.g. HT, of - this is a big problem and requires - long transmission paths also requires - circuits</li> <li>Synchronous: multiple options</li> </ul>                                                                                                                                                                                                                                                                                               |                                                                                    |

| <ul> <li>this is a big problem and requires</li> <li>long transmission paths also requires</li> <li>circuits</li> <li>Synchronous: multiple options</li> </ul>                                                                                                                                                                                                                                                                                                                        | PI. etc.)                                                                          |

| <ul> <li>long transmission paths also required</li> <li>Synchronous: multiple options</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                      | complex and energy hungry circuitry                                                |

| Synchronous: multiple options                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ire significant pre- and post-emphasi                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                    |

| • Tx side clock – source synchrone                                                                                                                                                                                                                                                                                                                                                                                                                                                    | us signaling                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                    |

| School of Computing<br>University of Utah                                                                                                                                                                                                                                                                                                                                                                                                                                             | CS 5780                                                                            |

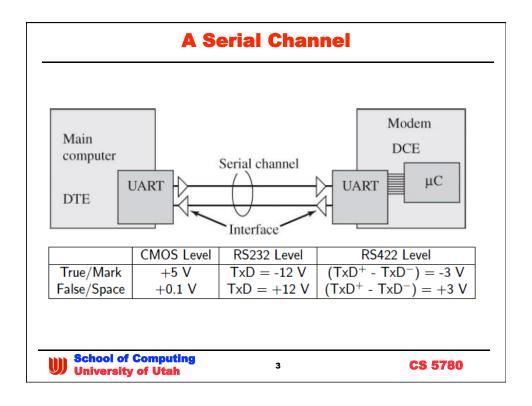

| Pin | Signal | Description         | True | DTE    | DCE |

|-----|--------|---------------------|------|--------|-----|

| 1   | DCD    | Data Carrier Detect | +12  | In     | Out |

| 2   | RxD    | Receive Data        | -12  | In     | Out |

| 3   | TxD    | Transmit Data       | -12  | Out    | In  |

| 4   | DTR    | Data Terminal Rdy   | +12  | Out    | In  |

| 5   | SG     | Signal Ground       |      |        |     |

| 6   | DSR    | Data Set Ready      | +12  | In     | Out |

| 7   | RTS    | Request to Send     | +12  | Out In | In  |

| 8   | CTS    | Clear to Send       | +12  | In     | Out |

| 9   | RI     | Ring Indicator      | +12  | In     | Out |

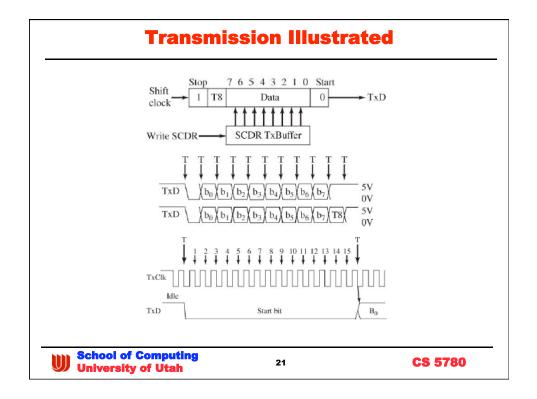

| TRANSMIT | Set TxD=0           | Output start bit  |

|----------|---------------------|-------------------|

|          | Wait 16 clock times | -                 |

|          | Set n=0             | Bit counter       |

| TLOOP    | Set TxD=bn          | Output data bit   |

|          | Wait 16 clock times | Wait 1 bit time   |

|          | Set n=n+1           |                   |

|          | Goto TLOOP if n<=7  |                   |

|          | Set TxD=T8          | Output T8 bit     |

|          | Wait 16 clock times | Wait 1 bit time   |

|          | Set TxD=1           | Output a stop bit |

|          | Wait 16 clock times | Wait 1 bit time   |

|          |                     |                   |

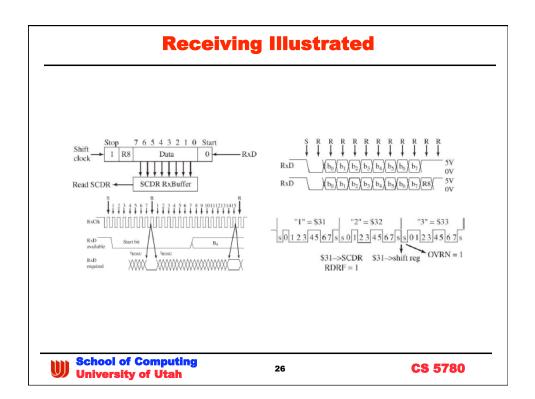

| Pse                  | udo Code fo                                                           | or Receive                                         | Process                    |

|----------------------|-----------------------------------------------------------------------|----------------------------------------------------|----------------------------|

| RECEIVE              | Wait 8 clock tin                                                      | RxD=1 Wait for<br>nes Wait hal:<br>RxD=1 False sta | f a bit time               |

| RLOOP                | Wait 16 clock t:<br>Set bn=RxD<br>Set n=n+1<br>Goto RLOOP if n        | Input dat                                          |                            |

|                      | Wait 16 clock t:<br>Set R8=RxD<br>Wait 16 clock t:<br>Set FE=1 if RxD | imes Wait 1 b:<br>Read R8 1<br>imes Wait 1 b:      | bit<br>it time<br>error if |

| School of University |                                                                       | 27                                                 | CS 5780                    |

| 9\$120                                    | 32 SCI Detail                 | S             |

|-------------------------------------------|-------------------------------|---------------|

| One SCI port using Por                    | t S bits 1 and 0.             |               |

| Least significant 13 bits                 | s of SCIBD register deter     | rmine baud    |

| rate.                                     |                               |               |

| SCICR2 register contai                    | ins control bits for SCI (s   | ee Table      |

| 7.11).                                    |                               |               |

| SCICR1 register contai                    | ins other miscellaneous S     | CI control    |

| bits.                                     |                               |               |

| LOOPS: disconnect                         | s receiver from RxD pin.      |               |

| RSRC: when LOOF                           | PS=1, RSRC=0 connects         | receiver to   |

| transmitter internally                    | y while RSRC=1 connects       | receiver to   |

| TxD.                                      |                               |               |

|                                           | on IDLE line, 1 wakeup on a   |               |

|                                           | dle line count starts from st | -             |

| SWAI: setting this the communication.     | bit causes SCI to shutdown    | and pause any |

| PE: setting this bit                      | enables parity checking.      |               |

| PT: 0 is even parity                      | while 1 is odd parity.        |               |

| School of Computing<br>University of Utah | 28                            | CS 5780       |

|                              | SPI Pseudo Code                                | 8                         |

|------------------------------|------------------------------------------------|---------------------------|

|                              | a                                              | -                         |

| TRANSMIT<br>TLOOP            |                                                | Bit counter<br>Output bit |

|                              | Set Data=1                                     | Idle output               |

| RECEIVE<br>RLOOP             | Set n=7<br>On rise of Sck, read data           | Bit counter               |

|                              | Set bn=Data<br>Set n=n-1<br>Goto RLOOP if n>=0 | Input bit                 |

|                              |                                                |                           |

| School of Co<br>University o |                                                | <b>CS 5780</b>            |

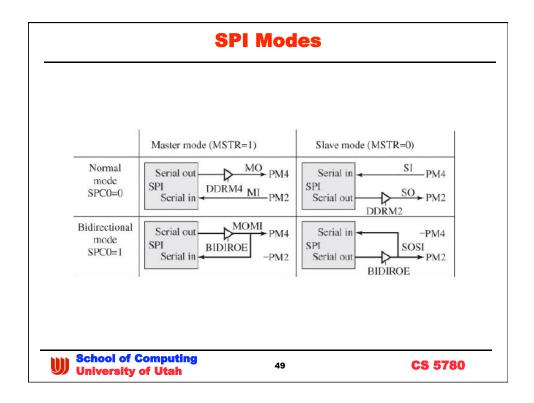

| MODFEN        | SSOE | Master N                                                         | /lode (MST   | R=1) Slave M  | ode (MSTR=0)   |

|---------------|------|------------------------------------------------------------------|--------------|---------------|----------------|

| 0             | 0    | PM3 not                                                          | used with SP | I PM3 is S    | S input        |

| 0             | 1    | PM3 not used with SPI PM3 is $\overline{SS}$ input               |              |               | 5 input        |

| 1             | 0    | PM3 is $\overline{SS}$ input w/MODF PM3 is $\overline{SS}$ input |              |               | <u>S</u> input |

| 1             | 1    | PM3 is $\overline{SS}$ output PM3 is $\overline{SS}$ input       |              |               |                |

| Pin Mode      | MSTR | SPC0                                                             | BIDIROE      | MISO          | MOSI           |

| Normal        | 1    | 0                                                                | Х            | Master In     | Master Out     |

| Bidirectional | 1    | 1                                                                | 0            | MISO not used | Master In      |

|               |      |                                                                  | 1            |               | Master I/O     |

| Normal        | 0    | 0                                                                | Х            | Slave Out     | Slave In       |

| Bidirectional | 0    | 1                                                                | 0            | Slave In      | MOSI not used  |

|               |      |                                                                  | 1            | Slave I/O     |                |

|               |      |                                                                  |              |               |                |