# **Remaining Interrupts** Vector Address 0xFFDE, 0xFFDF 0xFFDC, 0xFFDD 0xFFDA, 0xFFDB 0xFFD8, 0xFFD9 0xFFD6, 0xFFD7 0xFFD4, 0xFFD5 .. ortuRt (SPIE, SPTIE) 0x00D8 1 bit SCICR2 (TIE, TCIE, RIE, IUE) 0x00D8 Reserved not needed for Lab5 or this lecture OxFFC8, OxFFC9 OxFFC8, OxFFC7 OxFFC4, OxFFC5 OxFFBA to OxFFC3 OxFFB8, OxFFB9 CRG self clock mod Port P CS 5780

### **Setting up the TCB** struct TCB { struct TCB \*Next; /\* Link to Next TCB \*/ /\* Stack Pointer when idle \*/ unsigned char \*SP; unsigned short Id; /\* output to PortT \*/ unsigned char MoreStack[49]; /\* more stack \*/ unsigned char CCR; /\* Initial CCR \*/ unsigned char RegB; /\* Initial RegB \*/ /\* Initial RegA \*/ unsigned char RegA; unsigned short RegX; /\* Initial RegX \*/ unsigned short RegY; /\* Initial RegY \*/ void (\*PC)(void); /\* Initial PC \*/ typedef struct TCB TCBType; typedef TCBType \* TCBPtr; see anything fishy so far? School of Computing University of Utah CS 5780

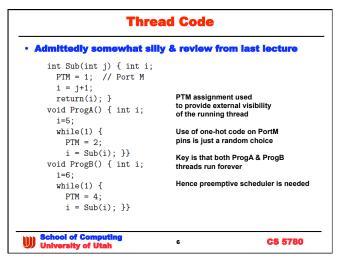

### Port M vs. Port T Essential difference between program & thread · program is just the code » note that code has no state » It's just a specification of what will happen if it is executed thread is an execution instance » Inherently has state · In this case initial state can be seen in the code subsequent state will depend TCB values if the thread isn't running TCB values and registers if the thread is runn • In this simple example • Port M is used to show which Program is being executed Port T is used to show which Thread is being executed · In this case » M will be the same for threads 1 & 2 » in general • a thread could run more than 1 program in different thread phases School of Computing University of Utah

8

```

Defining 3 Threads

TCBType sys[3]={

&sys[1],

&sys[0].CCR,

/* Pointer to Next */

/* Initial SP */

Thread n = sys[n]

1,

{ 0},

threads 1 & 2 are the same code

/* CCR,B,A,X,Y */

/* Initial PC */

0x40,0,0,0,0,

but work on different local data

ProgA },

{ &sys[2],

&sys[1].CCR,

/* Pointer to Next */

/* Initial SP */

CCR = 0x40

XIRQ disabled

/* Id */

IRQ enabled

{ 0},

0x40,0,0,0,0,

/* CCR,B,A,X,Y */

/* Initial PC */

Note all TCB variables values here influence only what happens the

ProgA },

{ &sys[0],

/* Pointer to Next */

FIRST time the thread is executed

&sys[2].CCR,

/* Initial SP */

/* Id */

Why will these variables need to be changed for subsequent executions?

{ 0},

0x40,0,0,0,0,

/* CCR,B,A,X,Y */

ProgB } };

/* Initial PC */

CS 5780

```

```

Preemptive Thread Scheduler in C

/* Pointer to current thread */

void main(void) {

DDRT = OxFF;

DDRM = OxFF;

/* Output running thread on Port T */

/* Output running program on Port M */

/* Specify first thread */

RunPt = &sys[0];

asm sei

TFLG1 = 0x20;

TIE = 0x20;

/* Clear C5F */

/* Arm C5F */

TSCR1 = 0x80;

TSCR2 = 0x01;

TIOS |= 0x20;

/* Enable TCNT*/

/* 2MHz TCNT */

/* Output compare */

TC5 = TCNT+20000;

PTT = RunPt->Id;

asm ldx RunPt

asm lds 2,x

asm cli

asm rti

/* Launch First Thread */

10

CS 5780

```

### **Preemptive Thread Switch** void interrupt 13 ThreadSwitch() { asm ldx RunPt asm sts 2,x RunPt = RunPt->Next; PTT = RunPt->Id; /\* PortH=active thread \*/ ldx RunPt asmlds 2,x TC5 = TCNT + 20000;/\* Thread runs for 10 ms \*/ TFLG1 = 0x20;/\* ack by clearing C5F \*/ see any mistakes? what does "interrupt 13" mean? School of Computing University of Utah 11 CS 5780

```

Dynamic Thread Allocator

NewPt->SP = &(NewPt->CCR); /* Stack Pointer when not running */

NewPt->Id = TheId;

NewPt->CCR = 0x40;

NewPt->RegB = 0;

NewPt->RegA = 0;

/* Visualize active thread */

/* Initial CCR, I=0 */

/* Initial RegB */

/* Initial RegA */

NewPt->RegX = 0;

NewPt->RegY = 0;

/* Initial RegX */

/* Initial RegY */

NewPt->PC = startFunc;

if(RunPt) {

/* Initial PC */

NewPt->Next = RunPt->Next;

RunPt->Next = NewPt;}

/* will run Next */

else

/* the first and only thread */

return SUCCESS:

School of Computi

University of Utah

12

CS 5780

```

### **Concluding Remarks**

- Implementation of a very simple thread system

- e.g. round robin preemptive

- · It's not that hard

- » but note the tricks for setting the PC to the appropriate thread code start

- Preemptive scheduling

- · lies at the heart of an RTOS

- » but in this case we didn't consider real time issues

- · making things significantly easier

- The hard part

- designing correct embedded codes that use threads

- Note

- · this code shows the general idea

- there are parts missing that will need to be coded for a full solution future lab?

School of Computing University of Utah

CS 5780

### So Far

- We've talked about

- thread scheduling

- synchronization

- » between main & ISR's

- Next

- synchronization

- » between threads

- · table driven scheduling

CS 5780

### 2 Threads & a communication FIFO

```

int Fifo_Put(char data)

char *Ppt;

// BEGIN CRITICAL

Ppt=PutPt;

*(Ppt++)=data;

if (Ppt == &Fifo[FIFOSIZE]) Ppt = &Fifo[0];

if (Ppt == GetPt ) {

// END CRITICAL

return(0);

} else {

PutPt=Ppt;

// END CRITICAL

return(1);

}

what's missing?

```

15

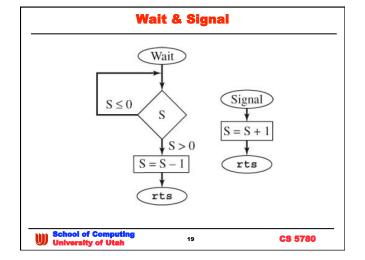

### **Semaphores**

- Used to implement mutual exclusion (MUTEX)

- · useful for sharing, synchronization, & com

- 2 basic operations

- · classic terminology

- » P → wait (Djikstra's Dutch "probeer te verlagen" ::- try to grab"

- » V → signal ("verhogen" ::= increase)

semaphore is binary value

- » 1 → free (resource available)

» 0 → busy (resource owned by some other thread)

- Numerous semaphore implementations

simplest is a "Spin-Lock" version

- - » thread calls wait to walt (spins) for sema ore to be free when semaphore is free, wait sets semaphore to busy

and then return

- enable interrupts during spin or preemption can't happen

read modify write on semaphore value must be atomic

otherwise as interrupt might write threads and chace will result

once thread is done it calls signal to return the semaphore to free

16

CS 5780

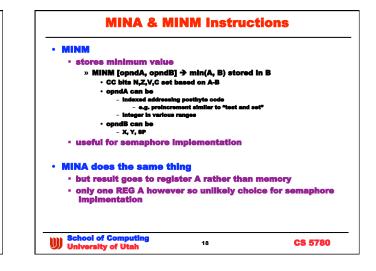

# Binary Simple lock Counter useful when multiple resources are available say tables in a restaurant oblive in a containing available olive of the place is busy hence the semantics Note earlier lecture error tst instruction is not "Test and Set" withis instruction exists on a lot of machines useful for binary semaphores 6812 TST, TSTA, TSTB → test M,A, or B for 0 or minus does not change M, A, or B value – just changes the CC flags hence not useful for semaphore implementation School of Computing University of Utah 17 CS 5780

**2 Common Semaphore Types**

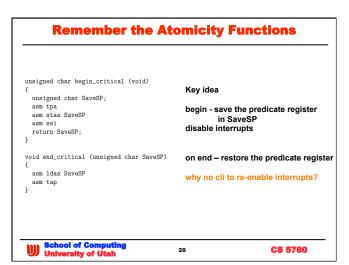

# // decrement and spin if less than 0 // input: pointer to a semaphore // output: none void OS\_Wait(short \*semaPt) { unsigned char SaveSP = begin\_critical(); while(\*semaPt <= 0) { end\_critical (SaveSP); asm nop SaveSP = begin\_critical(); } (\*semaPt)--; end\_critical (SaveSP); } key point: semaphore access is in critical section & MUTEX \*\*School of Computing \*\*Decrement and spin if less than 0 // input semaphore // output: none // output: n

```

// increment semaphore

// input: pointer to a semaphore

// output: none

void OS_Signal(short *semaPt) {

unsigned char SaveSP = begin_critical();

(*semaPt)++;

end_critical (SaveSP);

}

School of Computing

University of Utah

22 CS 5780

```

# **Spin-Lock Binary Semaphore**

23

School of Computing University of Utah

CS 5780

# **Counting Semaphore from Binary Semaphores**

24

CS 5780

Page 6

School of Computi

# void Wait(sema4Ptr semaphore) { $bWait(\&semaphore->s3); \hspace{0.2in} /\!/ \hspace{0.2in} wait \hspace{0.1in} if \hspace{0.1in} other \hspace{0.1in} caller \hspace{0.1in} here \hspace{0.1in} first \\$ (semaphore->value)--; // basic function of Wait if((semaphore->value)<0) {</pre> bSignal(&semaphore->s1); // end of exclusive access bWait(&semaphore->s2); // wait for value to go above 0

**Counting Semaphore (cont'd)**

7

bSignal(&semaphore->s1); // end of exclusive access bSignal(&semaphore->s3); // let other callers in

CS 5780

### **Counting Semaphore (cont'd)**

```

void Signal(sema4Ptr semaphore) {

bWait(&semaphore->s1);

// exclusive access

(semaphore->value)++;

// basic function of Signal

if((semaphore->value)<=0)

bSignal(&semaphore->s2); // allow S2 spinner to continue

bSignal(&semaphore->s1); // end of exclusive access

```

CS 5780

### **Blocking Semaphore**

• Useful when multiple threads are blocked waiting on a resource

27

School of Computing University of Utah

CS 5780

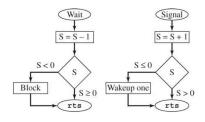

### **Blocking Semaphore Stages**

### Initialize:

Set the counter to its initial value. Clear associated blocked tcb linked list.

### Wait:

Disable interrupts to make atomic Decrement the semaphore counter, S=S-1 If semaphore counter < 0, then block this thread. Restore interrupt status.

### Signal:

Disable interrupts to make atomic Increment the semaphore counter, S=S+1If counter  $\leq$  0, wakeup one thread. Restore interrupt status

28

School of Computi University of Utah

```

Initialize

;semaphore counter

rmb 1

BlockPt rmb 2

;Pointer to threads blocked on S

Init

tpa

;Save old value of I

psha

sei

;Make atomic

ldaa #1

staa S

;Init semaphore value

ldx #Null

stx BlockPt ;empty list

pula

tap

;Restore old value of I

rts

CS 5780

```

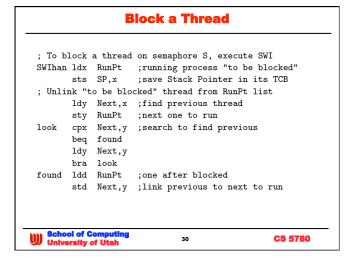

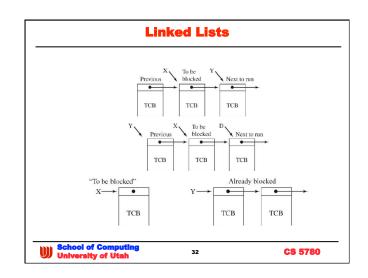

```

Block and Launch Next

; Put "to be blocked" thread on block list

ldy BlockPt

;link "to be blocked"

sty Next,x

stx BlockPt

; Launch next thread

ldx RunPt

lds SP,x

;set SP for this new thread

1dd TCNT

; Next thread gets a full 10ms time slice

addd #20000 ;interrupt after 10 ms

std TC5

ldaa #$20

staa TFLG1

;clear C5F

rti

School of Computing

University of Utah

CS 5780

31

```

### **Thread Rendezvous**

Synchronize two threads at a rendezvous location.

S1 S2 Meaning

- 0 Neither thread at rendezvous location

- -1 +1 Thread 2 arrived first, waiting for thread 1

- +1 -1 Thread 1 arrived first, waiting for thread 2

Thread 1 Thread 2 signal(&S1); signal(&S2); wait(&S2); wait(&S1);

This only works for 2 threads

How do you make a general n thread barrier?

CS 5780

### **Mutex Sharing or Non-reentrant Code**

Guarantee mutual exclusive access to a critical section. Thread 1 Thread 2 Thread 3 bwait(&S); bwait(&S); bwait(&S); printf("bye"); printf("tchau"); printf("ciao"); bsignal(&S); bsignal(&S); bsignal(&S);

CS 5780

### **2 Thread Mailbox**

Thread 1 sends mail to thread 2. Send Ack Meaning

0 0 No mail available, consumer not waiting -1 0 No mail available, consumer is waiting

35

-1 Mail available and producer is waiting +1

Producer thread Consumer thread wait(&send); signal(&send); read(Mail); wait(&ack); signal(&ack);

School of Computing University of Utah

CS 5780

### **Bounded FIFO**

Multiple consumer and producer threads

PutFifo GetFifo

wait(&RoomLeft); wait(&CurrentSize); wait(&mutex); wait(&mutex); put data in FIFO remove data from FIFO signal(&mutex); signal(&mutex); signal(&CurrentSize); signal(&RoomLeft); Could disable interrupts instead of using mutex, but would

lock out threads that don't affect the FIFO.

School of Computi

36

### **Concluding Remarks**

- Threads introduce concurrency

decoupling makes thinking about complex tasks easier

- there is a cost however

scheduling is required

scheduling is required

shared resources requires additional control

semaphores are the control mechanism

but access must be mutually exclusive

- Reminder

midterm Tuesday

- don't be late